CS313 Selected Lecture Notes

This is one big WEB page, used for printing

These are not intended to be complete lecture notes.

Complicated figures or tables or formulas are included here

in case they were not clear or not copied correctly in class.

Source code may be included in line or by a link.

Lecture numbers correspond to the syllabus numbering.

Lecture 1 Number Systems

Lecture 2 NASM

Lecture 3 Registers, Syntax and sections

Lecture 4 Arithmetic and shifting

Lecture 5 Using Debugger

Lecture 6 Branching and loops

Lecture 7 Subroutines and stacks

Lecture 8 Boot programs and 16-bit

Lecture 9 BIOS calls

Lecture 10 Hardware interface

Lecture 11 Privileged instructions

Lecture 12 Linux kernel calls

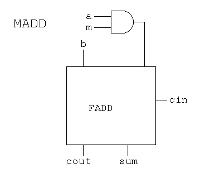

Lecture 13 Review

Lecture 14 Mid term exam

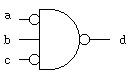

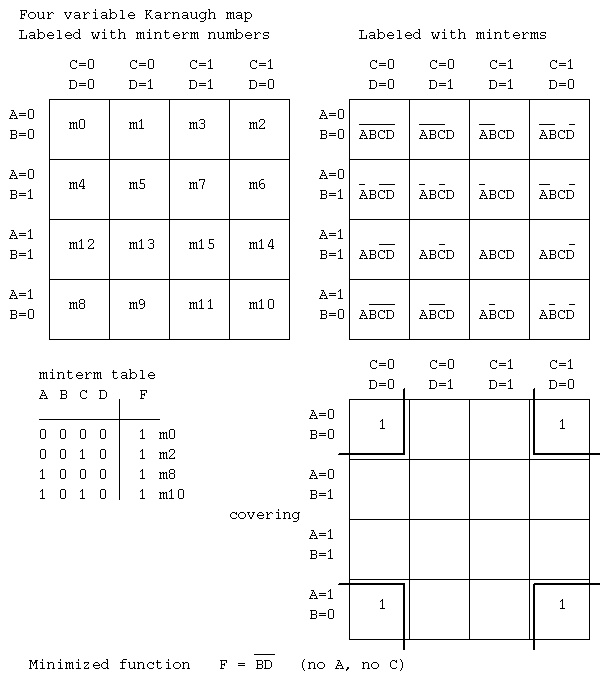

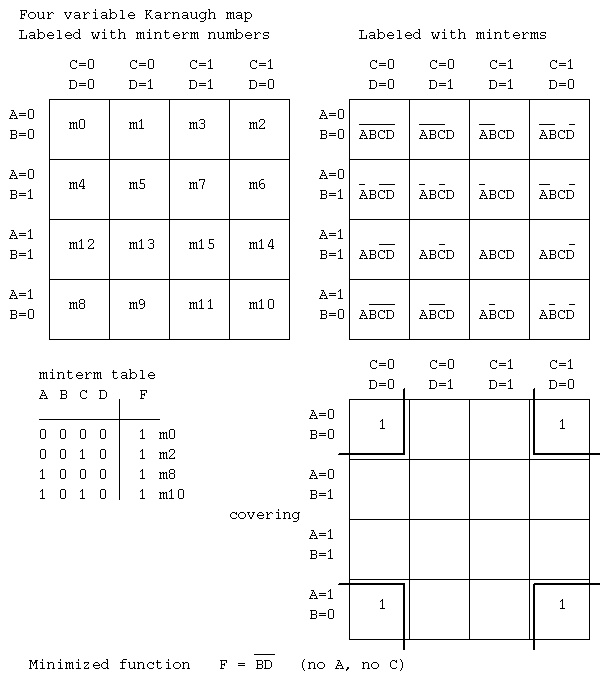

Lecture 15 Logic Gates

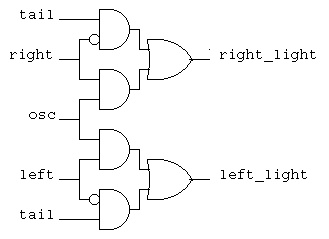

Lecture 16 Combinational logic

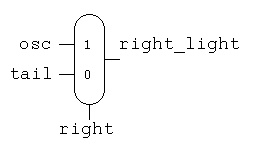

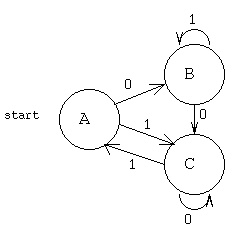

Lecture 17 Combinational logic design

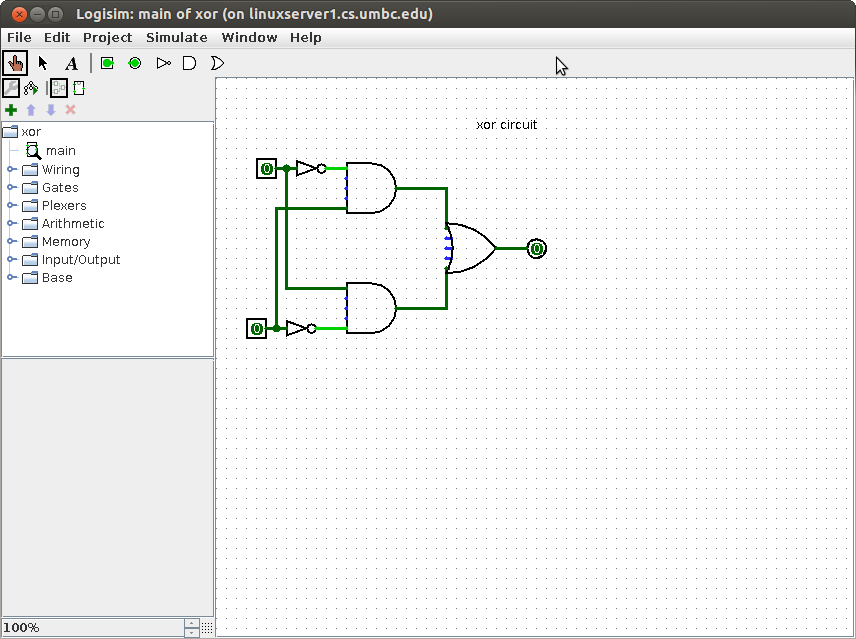

Lecture 18 Simulation tools

Lecture 19 Arithmetic circuits

Lecture 20 Multiply and divide

Lecture 21 Karnaugh maps, Quine McClusky

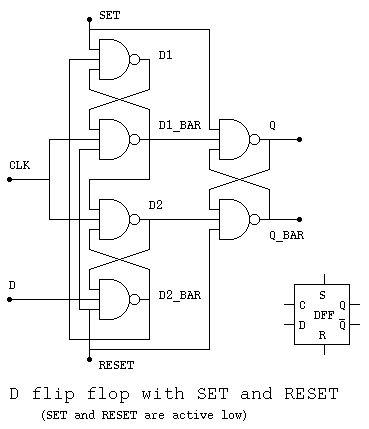

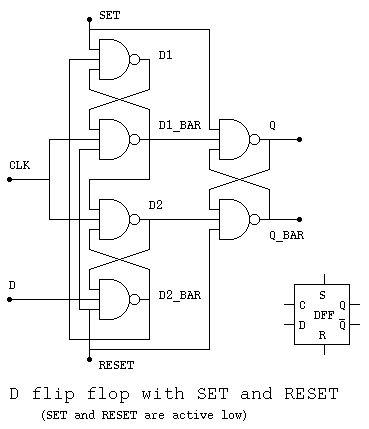

Lecture 22 Flip-flops, latches, registers

Lecture 23 Sequential logic

Lecture 24 Computer organization

Lecture 25 Instruction set

Lecture 26 Data Paths

Lecture 27 Arithematic Logic Unit

Lecture 28 Architecture

Lecture 29 Review

Lecture 30 Final Exam

Other Links

You should be familiar with programming.

You edit your source code and have it on the disc.

A compiler reads your source code and typically converts

high level language to assembly language as another file on the disc.

The assembler reads the assembly language and produces a

binary object file with machine instructions.

The loader reads object files and creates an executable image.

This course is to provide a basic understanding of how computers

operate internally, e.g. computer architecture and assembly language.

Technically: The computer does not run a "program", the computer

has an operating system that runs a "process". A process starts

with loading the executable image of a program in memory.

A process sets up "segments" of memory with:

A ".text" segment with computer instructions

A ".data" segment with initialized data

A ".rodata" segment with initialized data, read only

A ".bss" segment for variables and arrays, block starting symbols

A "stack" for pushing and popping values

A "heap" for dynamically getting more memory

And then the process is executed by having the program

address register set to the first executable instruction

in the process. You will be directly using segments in

your assembly language programs.

Computers store bits, binary digits, in memory and we usually

read the bits, four at a time as hexadecimal. The basic unit

of storage in the computer is two hex digits, eight bits, a byte.

The data may be integers, floating point or characters.

We start this course with a thorough understanding of numbers.

For Intel assembly language: two bytes are a word.

four bytes are a double word, eight bytes are a quad word.

Todays computers are almost all 64 bit machines,

we will be programming using 64 bit quad words.

Numbers are represented as the coefficients of powers of a base.

(in plain text, we use "^" to mean, raise to power or exponentiation)

With no extra base indication, expect decimal numbers:

12.34 is a representation of

1*10^1 + 2*10^0 + 3*10^-1 + 4*10^-2 or

10

2

.3

+ .04

------

12.34

Binary numbers, in NASM assembly language, have a trailing B or b.

101.11B is a representation of

1*2^2 + 0*2^1 + 1*2^0 + 1*2^-1 + 1*2^-2 or

4

0

1

.5 (you may compute 2^-n or look up in table below)

+ .25

------

5.75

Converting a decimal number to binary may be accomplished:

Convert 12.34 from decimal to binary

Integer part Fraction part

quotient remainder integer fraction

12/2 = 6 0 .34*2.0 = 0.68 use fmul, fistp get 0

6/2 = 3 0 .68*2.0 = 1.36 use fmul, fistp get 1

3/2 = 1 1 .36*2.0 = 0.72

1/2 = 0 1 .72*2.0 = 1.44

done .44*2.0 = 0.88

read up 1100 .88*2.0 = 1.76

.76*2.0 = 1.52

.52*2.0 = 1.04

quit

read down .01010111

answer is 1100.01010111

convert.c "C" program sample to do conversions

"C" program output

; in nasm assembly language make fistp truncate rather than round

fstcw WORD [cwd] ; store the FPU control word

or WORD [cwd],0x0c00 ; set rounding mode to "truncate"

fldcw WORD [cwd] ; load updated control word

hint:nasm storing a floating point fraction into an integer loacation, fistp

0.68 becomes 0

1.36 becomes 1

0.72 becomes 0

1.44 becomes 1

integer 34 to 34.0, 34.0/100.0 = .34 floating point

then multiply by 2.0

Powers of 2

Decimal

n -n

2 n 2

1 0 1.0

2 1 0.5

4 2 0.25

8 3 0.125

16 4 0.0625

32 5 0.03125

64 6 0.015625

128 7 0.0078125

256 8 0.00390625

512 9 0.001953125

1024 10 0.0009765625

2048 11 0.00048828125

4096 12 0.000244140625

8192 13 0.0001220703125

16384 14 0.00006103515625

32768 15 0.000030517578125

65536 16 0.0000152587890625

For binary to decimal:

2^3 2^2 2^1 2^0 2^-1 2^-2 2^-3

1 1 1 1 . 1 1 1

8 + 4 + 2 + 1 + .5 + .25 + .125 = 15.875

Binary

n -n

2 n 2

1 0 1.0

10 1 0.1

100 2 0.01

1000 3 0.001

10000 4 0.0001

100000 5 0.00001

1000000 6 0.000001

10000000 7 0.0000001

100000000 8 0.00000001

1000000000 9 0.000000001

10000000000 10 0.0000000001

100000000000 11 0.00000000001

1000000000000 12 0.000000000001

10000000000000 13 0.0000000000001

100000000000000 14 0.00000000000001

1000000000000000 15 0.000000000000001

10000000000000000 16 0.0000000000000001

Hexadecimal

n -n

2 n 2

1 0 1.0

2 1 0.8

4 2 0.4

8 3 0.2

10 4 0.1

20 5 0.08

40 6 0.04

80 7 0.02

100 8 0.01

200 9 0.008

400 10 0.004

800 11 0.002

1000 12 0.001

2000 13 0.0008

4000 14 0.0004

8000 15 0.0002

10000 16 0.0001

Decimal to Hexadecimal to Binary, 4 bits per hex digit

0 0 0000

1 1 0001

2 2 0010

3 3 0011

4 4 0100

5 5 0101

6 6 0110

7 7 0111

8 8 1000

9 9 1001

10 A 1010

11 B 1011

12 C 1100

13 D 1101

14 E 1110

15 F 1111

n n

n 2 hexadecimal 2 decimal approx notation

10 400 1,024 10^3 K kilo

20 100000 1,048,576 10^6 M mega

30 40000000 1,073,741,824 10^9 G giga

40 10000000000 1,099,511,627,776 10^12 T tera

The three representations of negative numbers that have been

used in computers are twos complement, ones complement and

sign magnitude. In order to represent negative numbers, it must

be known where the "sign" bit is placed. All modern binary

computers use the leftmost bit of the computer word as a sign bit.

The examples below use a 4-bit register to show all possible

values for the three representations.

decimal twos complement ones complement sign magnitude

0 0000 0000 0000

1 0001 0001 0001

2 0010 0010 0010

3 0011 0011 0011

4 0100 0100 0100

5 0101 0101 0101

6 0110 0110 0110

7 0111 0111 0111 all same for positive

-7 1001 1000 1111

-6 1010 1001 1110

-5 1011 1010 1101

-4 1100 1011 1100

-3 1101 1100 1011

-2 1110 1101 1010

-1 1111 1110 1001

-8 1000 -0 1111 -0 1000

^ / ^|||

\_ add 1 _/ sign__/ --- magnitude

To get the sign magnitude, convert the decimal to binary and

place a zero in the sign bit for positive, place a one in the

sign bit for negative.

To get the ones complement, convert the decimal to binary,

including leading zeros, then invert every bit. 1->0, 0->1.

To get the twos complement, get the ones complement and add 1.

(Throw away any bits that are outside of the register)

It may seem silly to have a negative zero, but it is

mathematically incorrect to have -(-8) = -8

Then, if you must use Roman Numerals roman.shtml

or roman_numeral.shtml

Size in bytes, names and power of 10 approximate power of 2 power.shtml

IEEE Floating point formats

Almost all Numerical Computation arithmetic is performed using

IEEE 754-1985 Standard for Binary Floating-Point Arithmetic.

The two formats that we deal with in practice are the 32 bit and

64 bit formats.

IEEE Floating-Point numbers are stored as follows:

The single format 32 bit has

1 bit for sign, 8 bits for exponent, 23 bits for fraction

The double format 64 bit has

1 bit for sign, 11 bits for exponent, 52 bits for fraction

There is actually a '1' in the 24th and 53rd bit to the left

of the fraction that is not stored. The fraction including

the non stored bit is called a significand.

The exponent is stored as a biased value, not a signed value.

The 8-bit has 127 added, the 11-bit has 1023 added.

A few values of the exponent are "stolen" for

special values, +/- infinity, not a number, etc.

Floating point numbers are sign magnitude. Invert the sign bit to negate.

Some example numbers and their bit patterns:

decimal

stored hexadecimal sign exponent fraction significand

bit in binary

The "1" is not stored

| biased

31 30....23 22....................0 exponent

2.0

40 00 00 00 0 10000000 00000000000000000000000 1.0 * 2^(128-127)

1.0

3F 80 00 00 0 01111111 00000000000000000000000 1.0 * 2^(127-127)

0.5

3F 00 00 00 0 01111110 00000000000000000000000 1.0 * 2^(126-127)

0.75

3F 40 00 00 0 01111110 10000000000000000000000 1.1 * 2^(126-127)

0.9999995

3F 7F FF FF 0 01111110 11111111111111111111111 1.1111* 2^(126-127)

0.1

3D CC CC CD 0 01111011 10011001100110011001101 1.1001* 2^(123-127)

The "1" is not stored

|

63 62...... 52 51 ..... 0

2.0

40 00 00 00 00 00 00 00 0 10000000000 000 ... 000 1.0 * 2^(1024-1023)

1.0

3F F0 00 00 00 00 00 00 0 01111111111 000 ... 000 1.0 * 2^(1023-1023)

0.5

3F E0 00 00 00 00 00 00 0 01111111110 000 ... 000 1.0 * 2^(1022-1023)

0.75

3F E8 00 00 00 00 00 00 0 01111111110 100 ... 000 1.1 * 2^(1022-1023)

0.9999999999999995

3F EF FF FF FF FF FF FF 0 01111111110 111 ... 1.11111* 2^(1022-1023)

0.1

3F B9 99 99 99 99 99 9A 0 01111111011 10011..1010 1.10011* 2^(1019-1023)

|

sign exponent fraction |

before storing subtract bias

Note that an integer in the range 0 to 2^23 -1 may be represented exactly.

Any power of two in the range -126 to +127 times such an integer may also

be represented exactly. Numbers such as 0.1, 0.3, 1.0/5.0, 1.0/9.0 are

represented approximately. 0.75 is 3/4 which is exact.

Some languages are careful to represent approximated numbers

accurate to plus or minus the least significant bit.

Other languages may be less accurate.

The operations of add, subtract, multiply and divide are defined as:

Given x1 = 2^e1 * f1

x2 = 2^e2 * f2 and e2 <= e1

x1 + x2 = 2^e1 *(f1 + 2^-(e1-e2) * f2) f2 is shifted then added to f1

x1 - x2 = 2^e1 *(f1 - 2^-(e1-e2) * f2) f2 is shifted then subtracted from f1

x1 * x2 = 2^(e1+e2) * f1 * f2

x1 / x2 = 2^(e1-e2) * (f1 / f2)

an additional operation is usually needed, normalization.

if the resulting "fraction" has digits to the left of the binary

point, then the fraction is shifted right and one is added to

the exponent for each bit shifted until the result is a fraction.

IEEE 754 Floating Point Standard

Strings of characters

We will use one of many character representations for

character strings, ASCII, one byte per character in a string.

symbol or name symbol or key stroke

key stroke

hexadecimal hexadecimal

decimal decimal

NUL ^@ 00 0 Spc 20 32 @ 40 64 ` 60 96

SOH ^A 01 1 ! 21 33 A 41 65 a 61 97

STX ^B 02 2 " 22 34 B 42 66 b 62 98

ETX ^C 03 3 # 23 35 C 43 67 c 63 99

EOT ^D 04 4 $ 24 36 D 44 68 d 64 100

ENQ ^E 05 5 % 25 37 E 45 69 e 65 101

ACK ^F 06 6 & 26 38 F 46 70 f 66 102

BEL ^G 07 7 ' 27 39 G 47 71 g 67 103

BS ^H 08 8 ( 28 40 H 48 72 h 68 104

TAB ^I 09 9 ) 29 41 I 49 73 i 69 105

LF ^J 0A 10 * 2A 42 J 4A 74 j 6A 106

VT ^K 0B 11 + 2B 43 K 4B 75 k 6B 107

FF ^L 0C 12 , 2C 44 L 4C 76 l 6C 108

CR ^M 0D 13 - 2D 45 M 4D 77 m 6D 109

SO ^N 0E 14 . 2E 46 N 4E 78 n 6E 110

SI ^O 0F 15 / 2F 47 O 4F 79 o 6F 111

DLE ^P 10 16 0 30 48 P 50 80 p 70 112

DC1 ^Q 11 17 1 31 49 Q 51 81 q 71 113

DC2 ^R 12 18 2 32 50 R 52 82 r 72 114

DC3 ^S 13 19 3 33 51 S 53 83 s 73 115

DC4 ^T 14 20 4 34 52 T 54 84 t 74 116

NAK ^U 15 21 5 35 53 U 55 85 u 75 117

SYN ^V 16 22 6 36 54 V 56 86 v 76 118

ETB ^W 17 23 7 37 55 W 57 87 w 77 119

CAN ^X 18 24 8 38 56 X 58 88 x 78 120

EM ^Y 19 25 9 39 57 Y 59 89 y 79 121

SUB ^Z 1A 26 : 3A 58 Z 5A 90 z 7A 122

ESC ^[ 1B 27 ; 3B 59 [ 5B 91 { 7B 123

LeftSh 1C 28 < 3C 60 \ 5C 92 | 7C 124

RighSh 1D 29 = 3D 61 ] 5D 93 } 7D 125

upAro 1E 30 > 3E 62 ^ 5E 94 ~ 7E 126

dnAro 1F 31 ? 3F 63 _ 5F 95 DEL 7F 127

Optional future installation on your personal computer

Throughout this course, we will be writing some assembly language.

This will be for an Intel or Intel compatible computer, e.g. AMD.

The assembler program is "nasm" and can be run on

linux.gl.umbc.edu or on your computer.

If you are running linux on your computer, the command

sudo apt-get install nasm

will install nasm on your computer.

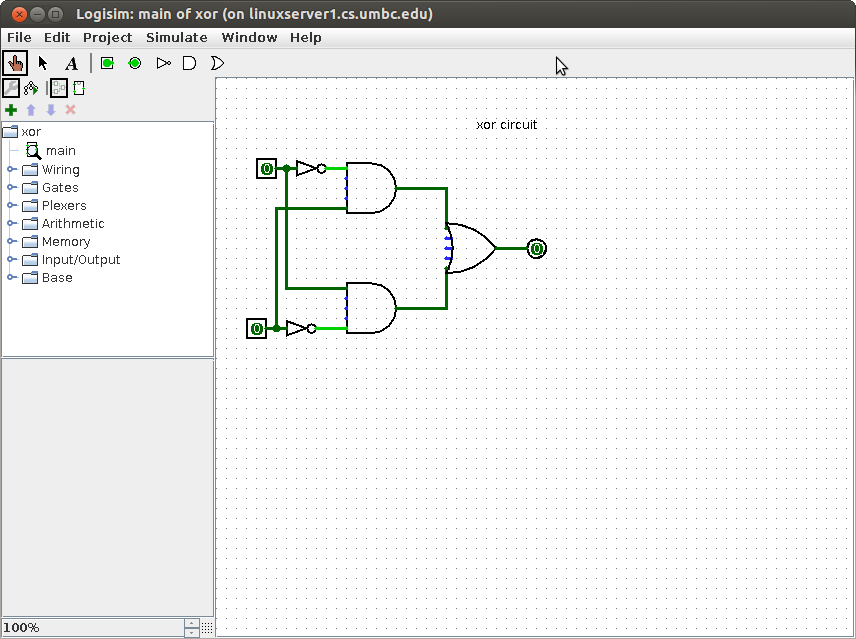

Throughout this course we will work with digital logic and

cover basic VHDL and verilog languages for describing

digital logic. There are free simulators, that will

simulate the operation of your digital logic for both languages

and graphical input simulator logisim.

The commands for installing these on linux are:

sudo apt-get install freehdl

or use Makefile_vhdl from my download directory on linux.gl.umbc.edu

sudo apt-get install iverilog

or use Makefile_verilog from my download directory on linux.gl.umbc.edu

from www.cburch.com/logisim/index.html get logisim

or use Makefile_logisim from my download directory on linux.gl.umbc.edu

These or similar programs may be available for installing

on some versions of Microsoft Windows or Mac OSX.

We will use 64-bit in this course, to expand your options.

In "C" int remains a 32-bit number although we have 64-bit computers

and 64-bit operating systems and 64-bit computers that are still

programmed as 32-bit computers.

test_factorial.c uses int, outputs:

test_factorial.c using int, note overflow

0!=1

1!=1

2!=2

3!=6

4!=24

5!=120

6!=720

7!=5040

8!=40320

9!=362880

10!=3628800

11!=39916800

12!=479001600

13!=1932053504 BAD

14!=1278945280

15!=2004310016

16!=2004189184

17!=-288522240

18!=-898433024

test_factorial_long.c uses long int, outputs:

test_factorial_long.c using long int, note overflow

0!=1

1!=1

2!=2

3!=6

4!=24

5!=120

6!=720

7!=5040

8!=40320

9!=362880

10!=3628800

11!=39916800

12!=479001600

13!=6227020800

14!=87178291200

15!=1307674368000

16!=20922789888000

17!=355687428096000

18!=6402373705728000

19!=121645100408832000

20!=2432902008176640000

21!=-4249290049419214848 BAD

22!=-1250660718674968576

Well, 13! wrong vs 21! wrong may not be a big deal.

factorial.py by default, outputs:

factorial(0)= 1

factorial(1)= 1

factorial(2)= 2

factorial(3)= 6

factorial(4)= 24

factorial(52)= 80658175170943878571660636856403766975289505440883277824000000000000

Yet, 32-bit signed numbers can only index 2GB of ram, 64-bit are

needed for computers with 4GB, 8GB, 16GB, 32GB etc of ram, available today.

95% of all supercomputers, called HPC, are 64-bit running Linux.

A first quick look at assembly language:

In high order language, A = B + C;

You think of adding the value of C to B and storing in A

In assembly language you think of A, B, and C as addresses.

You load the contents of address B into a register.

You add the contents of address C to that register.

You store that register at address A.

Well, Intel uses the word move, typed mov, for load and store.

mov rax,[B] ; semicolon starts a comment (no end of statement symbol)

add rax,[C] ; the [ ] says "contents of address"

mov [A],rax ; the mov is from second field to first field

; hello_64.asm print a string using printf

; Assemble: nasm -f elf64 -l hello_64.lst hello_64.asm

; Link: gcc -m64 -o hello_64 hello_64.o

; Run: ./hello_64 > hello_64.out

; Output: cat hello_64.out

; Equivalent C code

; // hello.c

; #include <stdio.h>

; int main()

; {

; char msg[] = "Hello world";

; printf("%s\n",msg);

; return 0;

; }

; Declare needed C functions

extern printf ; the C function, to be called

section .data ; Data section, initialized variables

msg: db "Hello world", 0 ; C string needs 0

fmt: db "%s", 10, 0 ; The printf format, "\n",'0'

section .text ; Code section.

global main ; the standard gcc entry point

main: ; the program label for the entry point

push rbp ; set up stack frame, must be aligned

mov rdi,fmt ; address of format, standard register rdi

mov rsi,msg ; address of first data, standard register rsi

mov rax,0 ; or can be xor rax,rax

call printf ; Call C function

; printf can mess up many registers

; save and reload registers with debug print

pop rbp ; restore stack

mov rax,0 ; normal, no error, return value

ret ; return

hello_64.lst with many comments removed

20 section .data ; Data section, initialized variables

21 00000000 48656C6C6F20776F72- msg: db "Hello world", 0 ; C string needs 0

22 00000009 6C6400

23 0000000C 25730A00 fmt: db "%s", 10, 0 ; The printf format, "\n",'0'

24

25 section .text ; Code section.

26

27 global main ; the standard gcc entry point

28 main: ; the program label for the entry point

29 00000000 55 push rbp ; set up stack frame, must be aligned

30

31 00000001 48BF- mov rdi,fmt ; address of format, standard register rdi

32 00000003 [0C00000000000000]

33 0000000B 48BE- mov rsi,msg ; address of first data, standard register rsi

34 0000000D [0000000000000000]

35 00000015 B800000000 mov rax,0 ; or can be xor rax,rax

36 0000001A E8(00000000) call printf ; Call C function

37

38 0000001F 5D pop rbp ; restore stack

39

40 00000020 B800000000 mov rax,0 ; normal, no error, return value

41 00000025 C3 ret ; return

You do not need C, computers come with BIOS.

; bios1.asm use BIOS interrupt for printing

; Compiled and run using one Linux command line

; nasm -f elf64 bios1.asm && ld bios1.o && ./a.out

global _start ; standard ld main program

section .text

_start:

print1: mov rax,[ahal]

int 10h ; write character to screen.

mov rax,[ret]

int 10h ; write new line '\n'

mov rax,0

ret

ahal: dq 0x0E28 ; output to screen ah has 0E

ret: dq 0x0E0A ; '\n'

; end bios1.asm

First homework assigned

on web, www.cs.umbc.edu/~squire/cs313_hw.shtml

Due in one week. Best to do right after lecture.

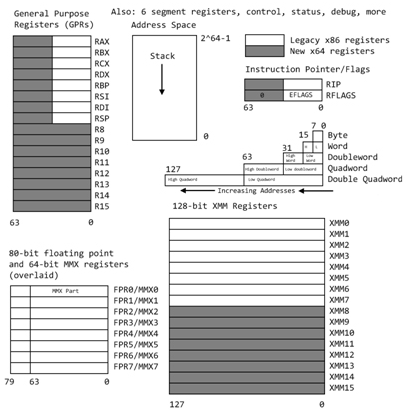

A 64-bit architecture, by definition, has 64-bit integer registers.

Here are sample programs and output to test for 64-bit capability in gcc:

Get sizeof on types and variables big.c

output from gcc -m64 big.c big.out

malloc more than 4GB big_malloc.c

output from big_malloc_mac.out

Newer Operating Systems and compilers

Get sizeof on types and variables big12.c

output from gcc big12.c big12.out

To bring everyone into the 64-bit world, we will use all 64-bit programs.

A note about the Intel computer architecture and the

tradeoff between "upward compatibility" and "clinging to the past".

Intel built a 4-bit computer 4004.

Intel built an 8-bit, byte, computer 8008

Intel built a 16-bit, word, computer 8086

Intel built a 32-bit, double word, computer 80386

Intel builds 64-bit, quad word, computers X86-64

The terms byte, word, double word, and quad word remain today

in the software we will write for modern 64-bit computers.

We use -f elf64 and -m64 for assembling and compiling

Learning a new programming language is an orderly progression

of steps.

1) Find sample code that you can compile and run to get output

This is typically hello_world or just hello

Then more output, we use "C" printf printf1.asm printf2.asm

2) Find sample code for defining data of the types supported

We use testdata_64.asm for Nasm assembly language

3) Find sample code to do integer arithmetic

We use intarith_64.asm

4) Find sample code to do floating point arithmetic

We use fltarith_64.asm

5) Find sample code to write a function and call a function

We use fib_64.asm or test_factorial.asm

Along the way, you will see the structure of typical code,

and initialization and termination of typical programs,

creating "if" and "loop" constructs. Then you can

"cut-and-paste" existing code, modify for your program.

Computer access for this course

NASM is installed on linux.gl.umbc.edu and can be used there.

From anywhere that you can reach the internet, log onto your

UMBC account using:

ssh your-user-id@linux.gl.umbc.edu

your-password

You should set up a directory for CMSC 313 and keep all your

course work in one directory.

e.g. mkdir cs313 # only once

cd cs313 # change to directory each time for CMSC 313

Copy over a sample program to your directory using:

cp /afs/umbc.edu/users/s/q/squire/pub/download/hello_64.asm .

Assemble hello.asm using:

nasm -f elf64 hello_64.asm

Link to create an executable using:

gcc -m64 -o hello hello_64.o

Execute the program using:

hello or ./hello

Assembly Language

Assembly Language is written as lines, rather than statements.

A semicolon makes the rest of a line a comment.

A line may be blank, a comment, a machine instruction or

an assembler directive called a pseudo instruction.

An optional label may start a line with a colon.

An assembly language program can run on a bare computer,

can run directly on an operating system, or can run using

a compiler and associated libraries. We will use a C compiler

and libraries for convenience.

A big difference between assembly language and compiler code

is that a label for a variable in assembly language is an address

while a name of a variable in compiler code is the value.

Assembly language programmers are very frugal.

They typically minimize storage space and time.

e.g. the instructions xor rax,rax mov rax,0 do the same

thing, zero register rax yet the xor is a little faster.

e.g. many variables are never stored in RAM, they keep values in registers.

I will avoid many of these "tricks" for a while.

(Files are available as hello.asm and hello_64.asm,

the _64 is to emphasize we will use all 64-bit values and registers.

Usually there is also a C language file, e.g. hello.c )

First example hello_64.asm

Now look at the file hello_64.asm

; hello_64.asm print a string using printf

; Assemble: nasm -f elf64 -l hello_64.lst hello_64.asm

; Link: gcc -m64 -o hello hello_64.o

; Run: ./hello > hello.out

; Output: cat hello.out

; Equivalent C code

; // hello.c

; #include <stdio.h>

; int main()

; {

; char msg[] = "Hello world";

; printf("%s\n",msg);

; return 0;

; }

; Declare needed C functions

extern printf ; the C function, to be called

section .data ; Data section, initialized variables

msg: db "Hello world", 0 ; C string needs 0

fmt: db "%s", 10, 0 ; The printf format, "\n",'0'

section .text ; Code section.

global main ; the standard gcc entry point

main: ; the program label for the entry point

push rbp ; set up stack frame, must be aligned

mov rdi,fmt ; pass format, standard register rdi

mov rsi,msg ; pass first parameter, standard register rsi

mov rax,0 ; or can be xor rax,rax

call printf ; Call C function

pop rbp ; restore stack

mov rax,0 ; normal, no error, return value

ret ; return

Makefile_nasm

Now, to save yourself typing, download Makefile_nasm into

your cs313 directory. There will be more sample files to download.

cp /afs/umbc.edu/users/s/q/squire/pub/download/Makefile_nasm Makefile

make # look in Makefile to see how to add more files to run

Type make # to run Makefile, only changed stuff gets run

Type make -f Makefile_nasm # only changed stuff gets run

Variable Data and Storage allocation, sections

There can be many types of data in the ".data" section:

Look at the file testdata_64.asm

and see the results in testdata_64.lst

; testdata_64.asm a program to demonstrate data types and values

; assemble: nasm -f elf64 -l testdata_64.lst testdata_64.asm

; link: gcc -m64 -o testdata_64 testdata_64.o

; run: ./testdata_64

; Look at the list file, testdata_64.lst

; no output

; Note! nasm ignores the type of data and type of reserved

; space when used as memory addresses.

; You may have to use qualifiers BYTE, WORD, DWORD or QWORD

section .data ; data section

; initialized, writeable

; db for data byte, 8-bit

db01: db 255,1,17 ; decimal values for bytes

db02: db 0xff,0ABh ; hexadecimal values for bytes

db03: db 'a','b','c' ; character values for bytes

db04: db "abc" ; string value as bytes 'a','b','c'

db05: db 'abc' ; same as "abc" three bytes

db06: db "hello",13,10,0 ; "C" string including cr and lf

; dw for data word, 16-bit

dw01: dw 12345,-17,32 ; decimal values for words

dw02: dw 0xFFFF,0abcdH ; hexadecimal values for words

dw03: dw 'a','ab','abc' ; character values for words

dw04: dw "hello" ; three words, 6-bytes allocated

; dd for data double word, 32-bit

dd01: dd 123456789,-7 ; decimal values for double words

dd02: dd 0xFFFFFFFF ; hexadecimal value for double words

dd03: dd 'a' ; character value in double word

dd04: dd "hello" ; string in two double words

dd05: dd 13.27E30 ; floating point value 32-bit IEEE

; dq for data quad word, 64-bit

dq01: dq 123456789012,-7 ; decimal values for quad words

dq02: dq 0xFFFFFFFFFFFFFFFF ; hexadecimal value for quad words

dq03: dq 'a' ; character value in quad word

dq04: dq "hello_world" ; string in two quad words

dq05: dq 13.27E300 ; floating point value 64-bit IEEE

; dt for data ten of 80-bit floating point

dt01: dt 13.270E3000 ; floating point value 80-bit in register

section .bss ; reserve storage space

; uninitialized, writeable

s01: resb 10 ; 10 8-bit bytes reserved

s02: resw 20 ; 20 16-bit words reserved

s03: resd 30 ; 30 32-bit double words reserved

s04: resq 40 ; 40 64-bit quad words reserved

s05: resb 1 ; one more byte

SECTION .text ; code section

global main ; make label available to linker

main: ; standard gcc entry point

push rbp ; initialize stack

mov al,[db01] ; correct to load a byte

mov ah,[db01] ; correct to load a byte

mov ax,[dw01] ; correct to load a word

mov eax,[dd01] ; correct to load a double word

mov rax,[dq01] ; correct to load a quad word

mov al,BYTE [db01] ; redundant, yet allowed

mov ax,[db01] ; no warning, loads two bytes

mov eax,[dw01] ; no warning, loads two words

mov rax,[dd01] ; no warning, loads two double words

; mov ax,BYTE [db01] ; error, size miss match

; mov eax,WORD [dw01] ; error, size miss match

; mov rax,WORD [dd01] ; error, size miss match

; push BYTE [db01] ; error, can not push a byte

push WORD [dw01] ; "push" needs to know size 2-byte

; push DWORD [dd01] ; error, can not push a 4-byte

push QWORD [dq01] ; OK

; push eax ; error, wrong size, need 64-bit

push rax

fld DWORD [dd05] ; floating load 32-bit

fld QWORD [dq05] ; floating load 64-bit

mov rbx,0 ; exit code, 0=normal

mov rax,1 ; exit command to kernel

int 0x80 ; interrupt 80 hex, call kernel

; end testdata_64.asm

Widen your browser window, part of testdata_64.lst

to see addresses and data values in hexadecimal.

1 ; testdata_64.asm a program to demonstrate data types and values

2 ; assemble: nasm -f elf64 -l testdata_64.lst testdata_64.asm

3 ; link: gcc -m64 -o testdata_64 testdata_64.o

4 ; run: ./testdata_64

5 ; Look at the list file, testdata_64.lst

6 ; no output

7 ; Note! nasm ignores the type of data and type of reserved

8 ; space when used as memory addresses.

9 ; You may have to use qualifiers BYTE, WORD, DWORD or QWORD

10

11 section .data ; data section

12 ; initialized, writeable

13

14 ; db for data byte, 8-bit

15 00000000 FF0111 db01: db 255,1,17 ; decimal values for bytes

16 00000003 FFAB db02: db 0xff,0ABh ; hexadecimal values for bytes

17 00000005 616263 db03: db 'a','b','c' ; character values for bytes

18 00000008 616263 db04: db "abc" ; string value as bytes 'a','b','c'

19 0000000B 616263 db05: db 'abc' ; same as "abc" three bytes

20 0000000E 68656C6C6F0D0A00 db06: db "hello",13,10,0 ; "C" string including cr and lf

21

22 ; dw for data word, 16-bit

23 00000016 3930EFFF2000 dw01: dw 12345,-17,32 ; decimal values for words

24 0000001C FFFFCDAB dw02: dw 0xFFFF,0abcdH ; hexadecimal values for words

25 00000020 6100616261626300 dw03: dw 'a','ab','abc' ; character values for words

26 00000028 68656C6C6F00 dw04: dw "hello" ; three words, 6-bytes allocated

27

28 ; dd for data double word, 32-bit

29 0000002E 15CD5B07F9FFFFFF dd01: dd 123456789,-7 ; decimal values for double words

30 00000036 FFFFFFFF dd02: dd 0xFFFFFFFF ; hexadecimal value for double words

31 0000003A 61000000 dd03: dd 'a' ; character value in double word

32 0000003E 68656C6C6F000000 dd04: dd "hello" ; string in two double words

33 00000046 AF7D2773 dd05: dd 13.27E30 ; floating point value 32-bit IEEE

34

35 ; dq for data quad word, 64-bit

36 0000004A 141A99BE1C000000F9- dq01: dq 123456789012,-7 ; decimal values for quad words

36 00000053 FFFFFFFFFFFFFF

37 0000005A FFFFFFFFFFFFFFFF dq02: dq 0xFFFFFFFFFFFFFFFF ; hexadecimal value for quad words

38 00000062 6100000000000000 dq03: dq 'a' ; character value in quad word

39 0000006A 68656C6C6F5F776F72- dq04: dq "hello_world" ; string in two quad words

39 00000073 6C640000000000

40 0000007A C86BB752A7D0737E dq05: dq 13.27E300 ; floating point value 64-bit IEEE

41

42 ; dt for data ten of 80-bit floating point

43 00000082 4011E5A59932D5B6F0- dt01: dt 13.270E3000 ; floating point value 80-bit in register

43 0000008B 66

44

45

46 section .bss ; reserve storage space

47 ; uninitialized, writeable

48

49 00000000 s01: resb 10 ; 10 8-bit bytes reserved

50 0000000A s02: resw 20 ; 20 16-bit words reserved

51 00000032 s03: resd 30 ; 30 32-bit double words reserved

52 000000AA s04: resq 40 ; 40 64-bit quad words reserved

53 000001EA s05: resb 1 ; one more byte

54

55 SECTION .text ; code section

56 global main ; make label available to linker

57 main: ; standard gcc entry point

58

59 00000000 55 push rbp ; initialize stack

60

61 00000001 8A0425[00000000] mov al,[db01] ; correct to load a byte

62 00000008 8A2425[00000000] mov ah,[db01] ; correct to load a byte

63 0000000F 668B0425[16000000] mov ax,[dw01] ; correct to load a word

64 00000017 8B0425[2E000000] mov eax,[dd01] ; correct to load a double word

65 0000001E 488B0425[4A000000] mov rax,[dq01] ; correct to load a quad word

66

67 00000026 8A0425[00000000] mov al,BYTE [db01] ; redundant, yet allowed

68 0000002D 668B0425[00000000] mov ax,[db01] ; no warning, loads two bytes

69 00000035 8B0425[16000000] mov eax,[dw01] ; no warning, loads two words

70 0000003C 488B0425[2E000000] mov rax,[dd01] ; no warning, loads two double words

71

72 ; mov ax,BYTE [db01] ; error, size miss match

73 ; mov eax,WORD [dw01] ; error, size miss match

74 ; mov rax,WORD [dd01] ; error, size miss match

75

76 ; push BYTE [db01] ; error, can not push a byte

77 00000044 66FF3425[16000000] push WORD [dw01] ; "push" needs to know size 2-byte

78 ; push DWORD [dd01] ; error, can not push a 4-byte

79 0000004C FF3425[4A000000] push QWORD [dq01] ; OK

80

81 ; push eax ; error, wrong size, need 64-bit

82 00000053 50 push rax

83

84 00000054 D90425[46000000] fld DWORD [dd05] ; floating load 32-bit

85 0000005B DD0425[7A000000] fld QWORD [dq05] ; floating load 64-bit

86

87 00000062 BB00000000 mov rbx,0 ; exit code, 0=normal

88 00000067 B801000000 mov rax,1 ; exit command to kernel

89 0000006C CD80 int 0x80 ; interrupt 80 hex, call kernel

90

91 ; end testdata_64.asm

You do not see much without output, we keep it simple

and use "C" printf.

printf1_64.asm

Then the output:

printf1_64.out

You can not do much without arithmetic, add, sub, mul, div

Example also shows the assembly language technique for a macro.

intarith_64.asm

Then the output:

intarith_64.out

Divide not exactly same as multiply.

Extreme macro.

div_test.asm

Then the output:

div_test.out

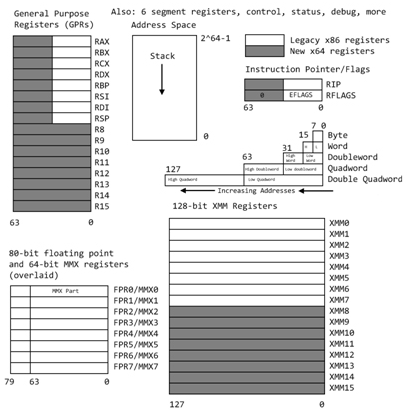

The next lecture will cover Intel registers:

The Intel x86-64 has many registers and named sub-registers.

This is why your 16-bit Intel programs will still run.

Here are some that are used in assembly language programming

and debugging (the "dash number" gives the number of bits):

Typically typed lower case.

+---------------------------------+ A register

|RAX-64 |

| +---------------------------+| RAX really extended accumulator

| | EAX-32 +-----------------+|| EAX extended extended accumulator

| | | AX-16 ||| Ax extended accumulator

| | |+--------+------+||| (A multiplicand before multiply)

| | || AH-8 | AL-8 |||| (A lower part of dividend before divide)

| | |+--------+------+||| (A lower part of product)

| | +-----------------+|| (H for high, L for low byte)

| +---------------------------+|

+---------------------------------+

+---------------------------------+ B register

|RBX-64 |

| +---------------------------+| RBX really extended base pointer

| | EBX-32 +-----------------+|| (EBX is double word segment)

| | | BX-16 ||| (BX is word segment)

| | |+--------+------+|||

| | || BH-8 | BL-8 ||||

| | |+--------+------+|||

| | +-----------------+||

| +---------------------------+|

+---------------------------------+

+---------------------------------+ C register

|RCX-64 |

| +---------------------------+| RCX 64-bit counter

| | ECX-32 +-----------------+|| (string and loop operations)

| | | CX-16 ||| (ECX is a 32 bit counter)

| | |+--------+------+||| (CX is a 16 bit counter)

| | || CH-8 | CL-8 |||| (see loop instruction)

| | |+--------+------+|||

| | +-----------------+||

| +---------------------------+|

+---------------------------------+

+---------------------------------+ D register

|RDX-64 |

| +---------------------------+| RDX extended EDX extended DX

| | EDX-32 +-----------------+|| (I/O pointer for memory mapped I/O)

| | | DX-16 ||| (D remainder after divide)

| | |+--------+------+||| (D upper part of dividend)

| | || DH-8 | DL-8 |||| (D upper part of product)

| | |+--------+------+|||

| | +-----------------+||

| +---------------------------+|

+---------------------------------+

+---------------------------------+ Stack Pointer

|RSP-64 |

| +---------------------------+| RSP 64-bit stack pointer

| | ESP-32 +-------------+|| ESP extended stack pointer

| | | SP-16 ||| SP stack pointer

| | +-------------+|| (used by PUSH and POP)

| +---------------------------+|

+---------------------------------+

+---------------------------------+ Base Pointer

|RBP-64 |

| +---------------------------+| RBP 64-bit base pointer

| | EBP-32 +-------------+|| EBP extended base pointer

| | | BP-16 ||| (by convention, callers stack)

| | +-------------+|| (BP in ES segment)

| +---------------------------+| We save it, push then pop

+---------------------------------+

+---------------------------------+ Source Index

|RSI-64 |

| +---------------------------+| RSI 64-bit source index

| | ESI-32 +-------------+|| ESI extended source index

| | | SI-16 ||| SI source index

| | +-------------+|| (SI in DS segment)

| +---------------------------+|

+---------------------------------+

+---------------------------------+ Destination Index

|RDI-64 |

| +---------------------------+| RDI 64-bit destination index

| | EDI-32 +-------------+|| EDI extended destination index

| | | DI-16 ||| DI destination index

| | +-------------+|| (DI in ES segment)

| +---------------------------+|

+---------------------------------+

+---------------------------------+ Instruction Pointer

|RIP-64 |

| +---------------------------+| RIP 64-bit instruction pointer

| | EIP-32 +-------------+|| EIP extended instruction pointer

| | | IP-16 ||| IP instruction pointer

| | +-------------+|| set by jump and call

| +---------------------------+|

+---------------------------------+

+---------------------------------+ Flags indicating errors

|RFLAGS-64 |

| +---------------------------+| RFLAGS 64-bit flags

| | EFLAGS-32 +-------------+|| EFLAGS extended flags

| | | FLAGS-16 ||| FLAGS

| | +-------------+|| (not a register name!)

| +---------------------------+| (must use PUSHF and POPF)

+---------------------------------+

Additional 64-bit registers are R8, R9, R10, R11, R12, R13, R14, R15

128-bit Registers for SSE instructions and printf are xmm0, ..., xmm15

Additional floating point stack, fld, fst, fstp, st0, st1, ... 80 bit

Use of registers and little endian

see testreg_64.asm for register syntax

see testreg_64.lst for binary encoding

Just a snippet of testreg_64.asm :

section .data ; preset constants, writeable

aa8: db 8 ; 8-bit

aa16: dw 16 ; 16-bit

aa32: dd 32 ; 32-bit

aa64: dq 64 ; 64-bit

section .text ; instructions, code segment

mov rax,[aa64] ; five registers in RAX

mov eax,[aa32] ; four registers in EAX

mov ax,[aa16]

mov ah,[aa8]

mov al,[aa8]

Just a snippet of testreg_64.lst

(line number, hex address in segment, hex data, assembly language)

((note byte 10 hex is 16 decimal, 20 hex is 32 decimal, etc))

((( note little endian, least significant byte first.)))

8 00000000 08 aa8: db 8

9 00000001 1000 aa16: dw 16

10 00000003 20000000 aa32: dd 32

11 00000007 4000000000000000 aa64: dq 64

24 00000001 488B0425[07000000] mov rax,[aa64]

25 00000009 8B0425[03000000] mov eax,[aa32]

26 00000010 668B0425[01000000] mov ax,[aa16]

27 00000018 8A2425[00000000] mov ah,[aa8]

28 0000001F 8A0425[00000000] mov al,[aa8]

OH! Did I forget to mention that Intel is a "little endian" machine.

The bytes are stored backwards to English.

The little end, least significant byte is first, smallest address.

Other registers that are extended include:

+-------------+ CS code segment

| CS-16 |

+-------------+

+-------------+ SS stack segment

| SS-16 |

+-------------+

+-------------+ DS data segment

| DS-16 | (current module)

+-------------+

+-------------+ ES data segment

| ES-16 | (calling module, destination string)

+-------------+

+-------------+ FS heap segment

| FS-16 |

+-------------+

+-------------+ GS global segment

| GS-16 | (shared)

+-------------+

There are also 80-bit or more, floating point registers ST0, ..., ST7

(These are actually a stack, note FST vs FSTP etc)

There are also control registers CR0, ..., CR4

There are also debug registers DR0, DR1, DR2, DR3, DR6, DR7

There are also test registers TR3, ...., TR7

Basic NASM syntax

The basic syntax for a line in NASM is:

label: opcode operand(s) ; comment

The "label" is a case sensitive user name, followed by a colon.

The label is optional and when not present, indent the opcode.

The label should start in column one of the line.

The label may be on a line with nothing else or a comment.

In assembly language the "label" is an address,

not a value as it is in compiler language.

The "opcode" is not case sensitive and may be a machine instruction

or an assembler directive (pseudo operation) or a macro call.

Typically, all "opcode" fields are neatly lined up starting in the

same column. Use of "tab" is OK.

Machine instructions may be preceded by a "prefix" such as:

a16, a32, o16, o32, and others.

"operand(s)" depend on the choice of "opcode".

An operand may have several parts separated by commas,

The parts may be a combination of register names, constants,

memory references in brackets [ ] or empty.

Comments are optional, yet encouraged.

Everything from the semicolon to the end of the line is

a comment, ignored by the assembler.

The semicolon may be in column one, making the entire line

a comment. Some editors put in two semicolon, no difference.

Sections or segments:

One specific assembler directive is the "section" or "SECTION"

directive. Four types of section are predefined for ELF format:

section .data ; initialized data

; writeable, not executable

; default alignment 8 bytes

section .bss ; uninitialized space for data

; writeable, not executable

; default alignment 8 bytes

section .rodata ; initialized data

; read only, not executable

; default alignment 8 bytes

section .text ; instructions (code)

; not writeable, executable

; default alignment 16 bytes

section other ; any name other than .data, .bss,

; .rodata, .text

; your stuff

; not executable, not writeable

; default alignment 1 byte

Efficiency and samples

A few comments on efficiency:

My experience is that a good assembly language programmer

can make a small (about 100 lines) "C" program more

efficient than the gcc compiler. But, for larger

programs, the compiler will be more efficient.

Exceptions are, for example, the SGI IRIX cc compiler

that has super optimization for that specific machine.

For the Intel x86-64 here are some samples in nasm and from gcc

(different syntax but you should be able to recognize the instructions)

Focus on the loop, there is prologue and epilogue code that should

be included, yet was omitted. Note the test has "check" values

at each end of the array. There is no range testing in

either "C" or assembly language.

A simple loop loopint_64.asm

; loopint_64.asm code loopint.c for nasm

; /* loopint_64.c a very simple loop that will be coded for nasm */

; #include <stdio.h>

; int main()

; {

; long int dd1[100]; // 100 could be 3 gigabytes

; long int i; // must be long for more than 2 gigabytes

; dd1[0]=5; /* be sure loop stays 1..98 */

; dd1[99]=9;

; for(i=1; i<99; i++) dd1[i]=7;

; printf("dd1[0]=%ld, dd1[1]=%ld, dd1[98]=%ld, dd1[99]=%ld\n",

; dd1[0], dd1[1], dd1[98],dd1[99]);

; return 0;

;}

; execution output is dd1[0]=5, dd1[1]=7, dd1[98]=7, dd1[99]=9

section .bss

dd1: resq 100 ; reserve 100 long int

i: resq 1 ; actually unused, kept in register

section .data ; Data section, initialized variables

fmt: db "dd1[0]=%ld, dd1[1]=%ld, dd1[98]=%ld, dd1[99]=%ld",10,0

extern printf ; the C function, to be called

section .text

global main

main: push rbp ; set up stack

mov qword [dd1],5 ; dd1[0]=5; memory to memory

mov qword [dd1+99*8],9 ; dd1[99]=9; indexed 99 qword

mov rdi, 1*8 ; i=1; index, will move by 8 bytes

loop1: mov qword [dd1+rdi],7 ; dd1[i]=7;

add rdi, 8 ; i++; 8 bytes

cmp rdi, 8*99 ; i<99

jne loop1 ; loop until incremented i=99

mov rdi, fmt ; pass address of format

mov rsi, qword [dd1] ; dd1[0] first list parameter

mov rdx, qword [dd1+1*8] ; dd1[1] second list parameter

mov rcx, qword [dd1+98*8] ; dd1[98] third list parameter

mov r8, qword [dd1+99*8] ; dd1[99] fourth list parameter

mov rax, 0 ; no xmm used

call printf ; Call C function

pop rbp ; restore stack

mov rax,0 ; normal, no error, return value

ret ; return

The simplest loop in NASM requires use of register rcx

"C" for(j=n; j>0; j--) // count down from n, do not use j==0

{

a[j] = 0.0;

}

section .data

n: dq 9

zero: dq 0.0

section .bss

a: resq 9

section .text

mov rcx, [n] ; j = 9; // start loop

jlab: fld qword [zero]

fstp qword [a+8*rcx] ; a[j] = 0.0; each a is 8 bytes

loop jlab ; j=j-1, jump to jlab: if j>0

A loop that counts up requires you to do the increment and compare:

"C" for(j=0; j<n; j++) // count up from zero, do not use j==n

{

a[j] = 0.0;

}

section .data

n: dq 9

zero: dq 0.0

section .bss

a: resq 9

section .text

mov rax,0 ; j = 0; // start loop

jlab: fld qword [zero]

fstp qword [a+8*rax] ; a[j] = 0.0; each a is 8 bytes

inc rax ; j = j + 1

cmp rax,[n] ; j <n ?

jl jlab ; jump to jlab: if j<n

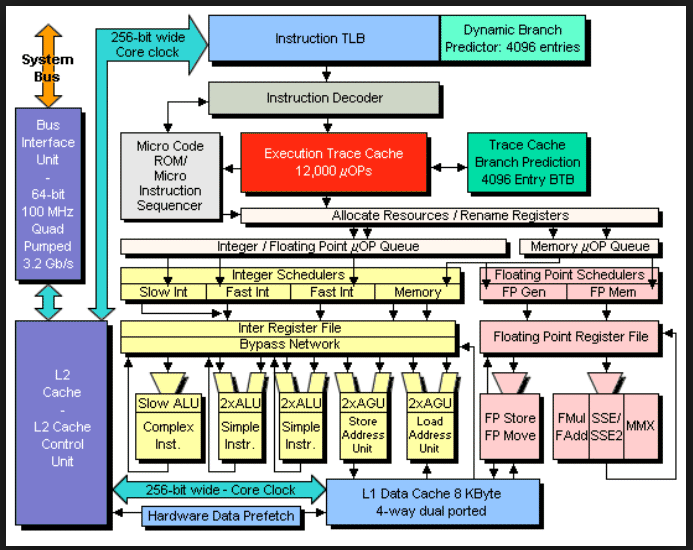

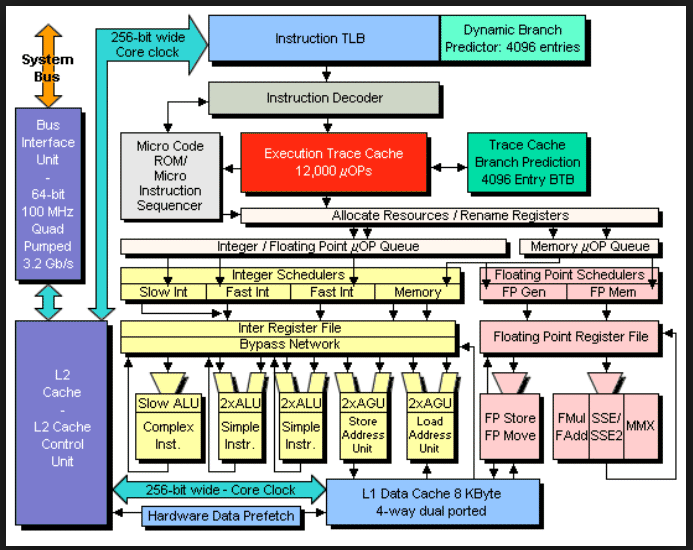

Speed consideration must take into account cache and virtual memory

performance, number of bytes transferred from RAM and clock cycles.

On modern computer architectures, this is almost impossible. For example,

the Pentium 4 translates the 80x86 code into RISC pipeline code and

is actually executing instructions that are different from the

assembly language. Carefully benchmarking complete applications is

about the only conclusive measure of efficiency.

"C" and other programming languages may call subroutines, functions,

procedures written in assembly language. Here is a small sample

using floating point just to show use of ST registers, mentioned in comments.

Main C program test_callf1_64.c

callf1_64.h

// test_callf1_64.c test callf1_64.asm

// nasm -f elf64 -l callf1_64.lst callf1_64.asm

// gcc -m64 -o test_callf1_64 test_callf1_64.c callf1_64.o

// ./test_callf1_64 > test_callf1_64.out

#include "callf1_64.h"

#include <stdio.h>

int main()

{

double L[2];

printf("test_callf1_64.c using callf1_64.asm\n");

L[0]=1.0;

L[1]=2.0;

callf1_64(L); // add 3.0 to L[0], add 4.0 to L[1]

printf("L[0]=%e, L[1]=%e \n", L[0], L[1]);

return 0;

}

Full with debug callf1_64.asm

Stripped down callf1_64.asm with no demo, no debug:

; callf1_64.asm a basic structure for a subroutine to be called from "C"

; Parameter: double *L

; Result: L[0]=L[0]+3.0 L[1]=L[1]+4.0

global callf1_64 ; linker must know name of subroutine

SECTION .data ; Data section, initialized variables

a3: dq 3.0 ; 64-bit variable a initialized to 3.0

a4: dq 4.0 ; 64-bit variable b initializes to 4.0

SECTION .text ; Code section.

callf1_64: ; name must appear as a nasm label

push rbp ; save rbp

mov rax,rdi ; first, only, in parameter, address

; add 3.0 to L[0]

fld qword [rax] ; load L[0] (pushed on flt pt stack, st0)

fadd qword [a3] ; floating add 3.0 (to st0)

fstp qword [rax] ; store into L[0] (pop flt pt stack)

fld qword [rax+8] ; load L[1] (pushed on flt pt stack, st0)

fadd qword [a4] ; floating add 4.0 (to st0)

fstp qword [rax+8] ; store into L[1] (pop flt pt stack)

pop rbp ; restore callers stack frame

ret ; return

We did not need to save floating point stack, we left it unchanged.

We could have used dt and tword for 80 bit floating point.

Calling printf uses xmm registers.

Simple loop using register rcx

loop_64.asm

loop_64_asm.out

; loop_64.asm simple using rcx and loop

; for(i=9; i>0; i++) A[i] = 0;

; Assemble: nasm -f elf64 loop_64.asm

; Link: gcc -m64 -o loop_64 loop_64.o

; Run: ./loop_64 > loop_64.out

; Output: cat hello_64.out

extern printf ; the C function, to be called

section .data ; Data section, initialized variables

fmt: db "A[%ld]=0", 10, 0 ; The printf format, "\n",'0'

section .bss

A: resq 10 ; A[0] .. A[9] in C A[0] unused

sav: resq 1 ; in case printf clobbers rcx

section .text ; Code section.

global main ; the standard gcc entry point

main: ; the program label for the entry point

push rbp ; set up stack frame, must be aligned

mov rcx,9

loop1: mov qword [A+rcx*8],0 ; A[i] = 0

mov [sav],rcx ; printf clobbers rcx debug printout

mov rdi,fmt ; address of format, standard register rdi

mov rsi,rcx ; address of first data, standard register rsi

mov rax,0 ; no float or double in xmm

call printf ; Call C function

mov rcx,[sav]

loop loop1 ; decrement rcx, jump if rcx > 0 zero

; [A+rcx*8-8] A[8] .. A[0]

pop rbp ; restore stack

mov rax,0 ; normal, no error, return value

ret ; return

output in loop_64_asm.out with -8 could be A[8]=0 .. A[0]=0

A[9]=0

A[8]=0

A[7]=0

A[6]=0

A[5]=0

A[4]=0

A[3]=0

A[2]=0

A[1]=0

A bunch of information, much you do not need, on nasm

nasmh.txt from nasm -h

Both integer and floating point arithmetic are demonstrated.

In order to make the source code smaller, a macro is defined

to print out results. The equivalent "C" program is given as

comments.

First, see how to call the "C" library function, printf, to make

it easier to print values:

Look at the file printf1_64.asm

; printf1_64.asm print an integer from storage and from a register

; Assemble: nasm -f elf64 -l printf1_64.lst printf1_64.asm

; Link: gcc -m64 -o printf1_64 printf1_64.o

; Run: ./printf1_64 > printf1_64.out

; Output: a=5, rax=7

; Equivalent C code

; /* printf1.c print a long int, 64-bit, and an expression */

; #include <stdio.h>

; int main()

; {

; long int a=5;

; printf("a=%ld, rax=%ld\n", a, a+2);

; return 0;

; }

; Declare external function

extern printf ; the C function, to be called

SECTION .data ; Data section, initialized variables

a: dq 5 ; long int a=5;

fmt: db "a=%ld, rax=%ld", 10, 0 ; The printf format, "\n",'0'

SECTION .text ; Code section.

global main ; the standard gcc entry point

main: ; the program label for the entry point

push rbp ; set up stack frame

mov rax,[a] ; put "a" from store into register

add rax,2 ; a+2 add constant 2

mov rdi,fmt ; format for printf

mov rsi,[a] ; first parameter for printf

mov rdx,rax ; second parameter for printf

mov rax,0 ; no xmm registers

call printf ; Call C function

pop rbp ; restore stack

mov rax,0 ; normal, no error, return value

ret ; return

Printing floating point

Now, we may need to print "float" and "double" and calling printf

gets more complicated. Still easier than doing your own conversion.

Look at the file printf2.asm

Output is printf2.out

; printf2_64.asm use "C" printf on char, string, int, long int, float, double

;

; Assemble: nasm -f elf64 -l printf2_64.lst printf2_64.asm

; Link: gcc -m64 -o printf2_64 printf2_64.o

; Run: ./printf2_64 > printf2_64.out

; Output: cat printf2_64.out

;

; A similar "C" program printf2_64.c

; #include <stdio.h>

; int main()

; {

; char char1='a'; /* sample character */

; char str1[]="mystring"; /* sample string */

; int len=9; /* sample string */

; int inta1=12345678; /* sample integer 32-bit */

; long int inta2=12345678900; /* sample long integer 64-bit */

; long int hex1=0x123456789ABCD; /* sample hexadecimal 64-bit*/

; float flt1=5.327e-30; /* sample float 32-bit */

; double flt2=-123.4e300; /* sample double 64-bit*/

;

; printf("printf2_64: flt2=%e\n", flt2);

; printf("char1=%c, srt1=%s, len=%d\n", char1, str1, len);

; printf("char1=%c, srt1=%s, len=%d, inta1=%d, inta2=%ld\n",

; char1, str1, len, inta1, inta2);

; printf("hex1=%lX, flt1=%e, flt2=%e\n", hex1, flt1, flt2);

; return 0;

; }

extern printf ; the C function to be called

SECTION .data ; Data section

; format strings for printf

fmt2: db "printf2: flt2=%e", 10, 0

fmt3: db "char1=%c, str1=%s, len=%d", 10, 0

fmt4: db "char1=%c, str1=%s, len=%d, inta1=%d, inta2=%ld", 10, 0

fmt5: db "hex1=%lX, flt1=%e, flt2=%e", 10, 0

char1: db 'a' ; a character

str1: db "mystring",0 ; a C string, "string" needs 0

len: equ $-str1 ; len has value, not an address

inta1: dd 12345678 ; integer 12345678, note dd

inta2: dq 12345678900 ; long integer 12345678900, note dq

hex1: dq 0x123456789ABCD ; long hex constant, note dq

flt1: dd 5.327e-30 ; 32-bit floating point, note dd

flt2: dq -123.456789e300 ; 64-bit floating point, note dq

SECTION .bss

flttmp: resq 1 ; 64-bit temporary for printing flt1

SECTION .text ; Code section.

global main ; "C" main program

main: ; label, start of main program

push rbp ; set up stack frame

fld dword [flt1] ; need to convert 32-bit to 64-bit

fstp qword [flttmp] ; floating load makes 80-bit,

; store as 64-bit

mov rdi,fmt2

movq xmm0, qword [flt2]

mov rax, 1 ; 1 xmm register

call printf

mov rdi, fmt3 ; first arg, format

mov rsi, [char1] ; second arg, char

mov rdx, str1 ; third arg, string

mov rcx, len ; fourth arg, int

mov rax, 0 ; no xmm used

call printf

mov rdi, fmt4 ; first arg, format

mov rsi, [char1] ; second arg, char

mov rdx, str1 ; third arg, string

mov rcx, len ; fourth arg, int

mov r8, [inta1] ; fifth arg, inta1 32->64

mov r9, [inta2] ; sixth arg, inta2

mov rax, 0 ; no xmm used

call printf

mov rdi, fmt5 ; first arg, format

mov rsi, [hex1] ; second arg, char

movq xmm0, qword [flttmp] ; first double

movq xmm1, qword [flt2] ; second double

mov rax, 2 ; 2 xmm used

call printf

pop rbp ; restore stack

mov rax, 0 ; exit code, 0=normal

ret ; main returns to operating system

Integer arithmetic

Now, for integer arithmetic, look at the file intarith_64.asm

Output is intarith_64.out

C version is intarith_64.c

Since all the lines use the same format, a macro was created

to do the call on printf.

; intarith_64.asm show some simple C code and corresponding nasm code

; the nasm code is one sample, not unique

;

; compile: nasm -f elf64 -l intarith_64.lst intarith_64.asm

; link: gcc -m64 -o intarith_64 intarith_64.o

; run: ./intarith_64 > intarith_64.out

;

; the output from running intarith.c is:

; c=5 , a=3, b=4, c=5

; c=a+b, a=3, b=4, c=7

; c=a-b, a=3, b=4, c=-1

; c=a*b, a=3, b=4, c=12

; c=c/a, a=3, b=4, c=4

;

;The file intarith.c is:

; /* intarith.c */

; #include <stdio.h>

; int main()

; {

; long int a=3, b=4, c;

; c=5;

; printf("%s, a=%ld, b=%ld, c=%ld\n","c=5 ", a, b, c);

; c=a+b;

; printf("%s, a=%ld, b=%ld, c=%ld\n","c=a+b", a, b, c);

; c=a-b;

; printf("%s, a=%ld, b=%ld, c=%ld\n","c=a-b", a, b, c);

; c=a*b;

; printf("%s, a=%ld, b=%ld, c=%ld\n","c=a*b", a, b, c);

; c=c/a;

; printf("%s, a=%ld, b=%ld, c=%ld\n","c=c/a", a, b, c);

; return 0;

; }

extern printf ; the C function to be called

%macro pabc 1 ; a "simple" print macro

section .data

.str db %1,0 ; %1 is first actual in macro call

section .text

mov rdi, fmt4 ; first arg, format

mov rsi, .str ; second arg

mov rdx, [a] ; third arg

mov rcx, [b] ; fourth arg

mov r8, [c] ; fifth arg

mov rax, 0 ; no xmm used

call printf ; Call C function

%endmacro

section .data ; preset constants, writeable

a: dq 3 ; 64-bit variable a initialized to 3

b: dq 4 ; 64-bit variable b initializes to 4

fmt4: db "%s, a=%ld, b=%ld, c=%ld",10,0 ; format string for printf

section .bss ; unitialized space

c: resq 1 ; reserve a 64-bit word

section .text ; instructions, code segment

global main ; for gcc standard linking

main: ; label

push rbp ; set up stack

lit5: ; c=5;

mov rax,5 ; 5 is a literal constant

mov [c],rax ; store into c

pabc "c=5 " ; invoke the print macro

addb: ; c=a+b;

mov rax,[a] ; load a

add rax,[b] ; add b

mov [c],rax ; store into c

pabc "c=a+b" ; invoke the print macro

subb: ; c=a-b;

mov rax,[a] ; load a

sub rax,[b] ; subtract b

mov [c],rax ; store into c

pabc "c=a-b" ; invoke the print macro

mulb: ; c=a*b;

mov rax,[a] ; load a (must be rax for multiply)

imul qword [b] ; signed integer multiply by b

mov [c],rax ; store bottom half of product into c

pabc "c=a*b" ; invoke the print macro

mulcx: ; c=b*b rcx;

mov rcx,[b] ; load b into rcx

imul rcx,[b] ; signed integer multiply by b

mov [c],rcx ; store bottom half of product into c

pabc "c=b*b rcx" ; invoke the print macro

mulbn: ; c=a*b;

mov rax,[a] ; load a (must be rax for multiply)

mul qword [b] ; signed integer multiply by b

mov [c],rax ; store bottom half of product into c

pabc "c=a*b mul" ; invoke the print macro

diva: ; c=c/a; both idiv and div allowed

mov rax,[c] ; load c

mov rdx,0 ; load upper half of dividend with zero

idiv qword [a] ; divide double register rdx rax by a

mov [c],rax ; store quotient into c

pabc "c=c/a" ; invoke the print macro

anda:

mov rax,[a] ; load a

and rax,1 ; logical and, bottom bit

mov [c],rax ; store result, just botton bit

pabc "c=a and 1 " ; invoke the print macro

; also available "or" "xor" "not"

shrb:

mov rax,[b] ; load b

shr rax,1 ; shift bits right 1 place

mov [c],rax ; store result, botton bit gone

pabc "c=b shr 1 " ; invoke the print macro

pop rbp ; pop stack

mov rax,0 ; exit code, 0=normal

ret ; main returns to operating system

Output running intarith_64.asm is:

c=5 , a=3, b=4, c=5

c=a+b, a=3, b=4, c=7

c=a-b, a=3, b=4, c=-1

c=a*b, a=3, b=4, c=12

c=b*b rcx, a=3, b=4, c=16

c=a*b mul, a=3, b=4, c=12

c=c/a, a=3, b=4, c=4

c=a and 1 , a=3, b=4, c=1

c=b shr 1 , a=3, b=4, c=2

Note that two registers are used for general multiply and divide.

bbbb [mem] a product of 64-bits times 64-bits is 128-bits

imul bbbb rax

---------

rdx bbbbbbbb rax the upper part of the product is in rdx

the lower part of the product is in rax

rdx bbbbbbbb rax before divide, the upper part of dividend is in rdx

the lower part of dividend is in rax

idiv bbbb [mem] the divisor

--------

after divide, the quotient is in rax

the remainder is in rdx

Floating point arithmetic

Now, for floating point arithmetic, look at the file fltarith_64.asm

Output is fltarith_64.out

C version is fltarith_64.c

Since all the lines use the same format, a macro was created

to do the call on printf.

Note the many similarities to integer arithmetic, yet some basic differences.

; fltarith_64.asm show some simple C code and corresponding nasm code

; the nasm code is one sample, not unique

;

; compile nasm -f elf64 -l fltarith_64.lst fltarith_64.asm

; link gcc -m64 -o fltarith_64 fltarith_64.o

; run ./fltarith_64 > fltarith_64.out

;

; the output from running fltarith and fltarithc is:

; c=5.0, a=3.000000e+00, b=4.000000e+00, c=5.000000e+00

; c=a+b, a=3.000000e+00, b=4.000000e+00, c=7.000000e+00

; c=a-b, a=3.000000e+00, b=4.000000e+00, c=-1.000000e+00

; c=a*b, a=3.000000e+00, b=4.000000e+00, c=1.200000e+01

; c=c/a, a=3.000000e+00, b=4.000000e+00, c=4.000000e+00

; a=i , a=8.000000e+00, b=1.600000e+01, c=1.600000e+01

; a<=b , a=8.000000e+00, b=1.600000e+01, c=1.600000e+01

; b==c , a=8.000000e+00, b=1.600000e+01, c=1.600000e+01

;The file fltarith.c is:

; #include <stdio.h>

; int main()

; {

; double a=3.0, b=4.0, c;

; long int i=8;

;

; c=5.0;

; printf("%s, a=%e, b=%e, c=%e\n","c=5.0", a, b, c);

; c=a+b;

; printf("%s, a=%e, b=%e, c=%e\n","c=a+b", a, b, c);

; c=a-b;

; printf("%s, a=%e, b=%e, c=%e\n","c=a-b", a, b, c);

; c=a*b;

; printf("%s, a=%e, b=%e, c=%e\n","c=a*b", a, b, c);

; c=c/a;

; printf("%s, a=%e, b=%e, c=%e\n","c=c/a", a, b, c);

; a=i;

; b=a+i;

; i=b;

; c=i;

; printf("%s, a=%e, b=%e, c=%e\n","c=c/a", a, b, c);

; if(a<b) printf("%s, a=%e, b=%e, c=%e\n","a<=b ", a, b, c);

; else printf("%s, a=%e, b=%e, c=%e\n","a>b ", a, b, c);

; if(b==c)printf("%s, a=%e, b=%e, c=%e\n","b==c ", a, b, c);

; else printf("%s, a=%e, b=%e, c=%e\n","b!=c ", a, b, c);

; return 0;

; }

extern printf ; the C function to be called

%macro pabc 1 ; a "simple" print macro

section .data

.str db %1,0 ; %1 is macro call first actual parameter

section .text

; push onto stack backwards

mov rdi, fmt ; address of format string

mov rsi, .str ; string passed to macro

movq xmm0, qword [a] ; first floating point in fmt

movq xmm1, qword [b] ; second floating point

movq xmm2, qword [c] ; third floating point

mov rax, 3 ; 3 floating point arguments to printf

call printf ; Call C function

%endmacro

section .data ; preset constants, writeable

a: dq 3.0 ; 64-bit variable a initialized to 3.0

b: dq 4.0 ; 64-bit variable b initializes to 4.0

i: dq 8 ; a 64 bit integer

five: dq 5.0 ; constant 5.0

fmt: db "%s, a=%e, b=%e, c=%e",10,0 ; format string for printf

section .bss ; unitialized space

c: resq 1 ; reserve a 64-bit word

section .text ; instructions, code segment

global main ; for gcc standard linking

main: ; label

push rbp ; set up stack

lit5: ; c=5.0;

fld qword [five] ; 5.0 constant

fstp qword [c] ; store into c

pabc "c=5.0" ; invoke the print macro

addb: ; c=a+b;

fld qword [a] ; load a (pushed on flt pt stack, st0)

fadd qword [b] ; floating add b (to st0)

fstp qword [c] ; store into c (pop flt pt stack)

pabc "c=a+b" ; invoke the print macro

subb: ; c=a-b;

fld qword [a] ; load a (pushed on flt pt stack, st0)

fsub qword [b] ; floating subtract b (to st0)

fstp qword [c] ; store into c (pop flt pt stack)

pabc "c=a-b" ; invoke the print macro

mulb: ; c=a*b;

fld qword [a] ; load a (pushed on flt pt stack, st0)

fmul qword [b] ; floating multiply by b (to st0)

fstp qword [c] ; store product into c (pop flt pt stack)

pabc "c=a*b" ; invoke the print macro

diva: ; c=c/a;

fld qword [c] ; load c (pushed on flt pt stack, st0)

fdiv qword [a] ; floating divide by a (to st0)

fstp qword [c] ; store quotient into c (pop flt pt stack)

pabc "c=c/a" ; invoke the print macro

intflt: ; a=i;

fild qword [i] ; load integer as floating point

fst qword [a] ; store the floating point (no pop)

fadd st0 ; b=a+i; 'a' as 'i' already on flt stack

fst qword [b] ; store sum (no pop) 'b' still on stack

fistp qword [i] ; i=b; store floating point as integer

fild qword [i] ; c=i; load again from ram (redundant)

fstp qword [c]

pabc "a=i " ; invoke the print macro

cmpflt: fld qword [b] ; into st0, then pushed to st1

fld qword [a] ; in st0

fcomip st0,st1 ; a compare b, pop a

jg cmpfl2

pabc "a<=b "

jmp cmpfl3

cmpfl2:

pabc "a>b "

cmpfl3:

fld qword [c] ; should equal [b]

fcomip st0,st1

jne cmpfl4

pabc "b==c "

jmp cmpfl5

cmpfl4:

pabc "b!=c "

cmpfl5:

pop rbp ; pop stack

mov rax,0 ; exit code, 0=normal

ret ; main returns to operating system

Shift data in a register

Refer to nasmdoc.txt for details.

A brief summary is provided here.

"reg" is an 8-bit, 16-bit or 32-bit or 64-bit register

"count" is a number of bits to shift

"right" moves contents of the register to the right, makes it smaller

"left" moves contents of the register to the left, makes it bigger

SAL reg,count shift arithmetic left

SAR reg,count shift arithmetic right (sign extension)

SHL reg,count shift left (logical, zero fill)

SHR reg,count shift right (logical, zero fill)

ROL reg,count rotate left

ROR reg,count rotate right

SHLD reg1,reg2,count shift left double-register

SHRD reg1,reg2,count shift right double-register

An example of using the various shifts is in: shift_64.asm

Output is shift_64.out

Just to make it easy to check, we keep all shift amounts a multiple

of 4, 4 bits per hex digit in output.

; shift_64.asm the nasm code is one sample, not unique

;

; compile: nasm -f elf64 -l shift_64.lst shift_64.asm

; link: gcc -m64 -o shift_64 shift_64.o

; run: ./shift_64 > shift_64.out

;

; the output from running shift.asm (zero filled) is:

; shl rax,4, old rax=ABCDEF0987654321, new rax=BCDEF09876543210,

; shl rax,8, old rax=ABCDEF0987654321, new rax=CDEF098765432100,

; shr rax,4, old rax=ABCDEF0987654321, new rax= ABCDEF098765432,

; sal rax,8, old rax=ABCDEF0987654321, new rax=CDEF098765432100,

; sar rax,4, old rax=ABCDEF0987654321, new rax=FABCDEF098765432,

; rol rax,4, old rax=ABCDEF0987654321, new rax=BCDEF0987654321A,

; ror rax,4, old rax=ABCDEF0987654321, new rax=1ABCDEF098765432,

; shld rdx,rax,8, old rdx:rax=0,ABCDEF0987654321,

; new rax=ABCDEF0987654321 rdx= AB,

; shl rax,8 , old rdx:rax=0,ABCDEF0987654321,

; new rax=CDEF098765432100 rdx= AB,

; shrd rdx,rax,8, old rdx:rax=0,ABCDEF0987654321,

; new rax=ABCDEF0987654321 rdx=2100000000000000,

; shr rax,8 , old rdx:rax=0,ABCDEF0987654321,

; new rax= ABCDEF09876543 rdx=2100000000000000,

extern printf ; the C function to be called

%macro prt 1 ; old and new rax

section .data

.str db %1,0 ; %1 is which shift string

section .text

mov rdi, fmt ; address of format string

mov rsi, .str ; callers string

mov rdx,rax ; new value

mov rax, 0 ; no floating point

call printf ; Call C function

%endmacro

%macro prt2 1 ; old and new rax,rdx

section .data

.str db %1,0 ; %1 is which shift

section .text

mov rdi, fmt2 ; address of format string

mov rsi, .str ; callers string

mov rcx, rdx ; new rdx befor next because used

mov rdx, rax ; new rax

mov rax, 0 ; no floating point

call printf ; Call C function

%endmacro

section .bss

raxsave: resq 1 ; save rax while calling a function

rdxsave: resq 1 ; save rdx while calling a function

section .data ; preset constants, writeable

b64: dq 0xABCDEF0987654321 ; data to shift

fmt: db "%s, old rax=ABCDEF0987654321, new rax=%16lX, ",10,0 ; format string

fmt2: db "%s, old rdx:rax=0,ABCDEF0987654321,",10," new rax=%16lX rdx=%16lX, ",10,0

section .text ; instructions, code segment

global main ; for gcc standard linking

main: push rbp ; set up stack

shl1: mov rax, [b64] ; data to shift

shl rax, 4 ; shift rax 4 bits, one hex position left

prt "shl rax,4 " ; invoke the print macro

shl4: mov rax, [b64] ; data to shift

shl rax,8 ; shift rax 8 bits. two hex positions left

prt "shl rax,8 " ; invoke the print macro

shr4: mov rax, [b64] ; data to shift

shr rax,4 ; shift

prt "shr rax,4 " ; invoke the print macro

sal4: mov rax, [b64] ; data to shift

sal rax,8 ; shift

prt "sal rax,8 " ; invoke the print macro

sar4: mov rax, [b64] ; data to shift

sar rax,4 ; shift

prt "sar rax,4 " ; invoke the print macro

rol4: mov rax, [b64] ; data to shift

rol rax,4 ; shift

prt "rol rax,4 " ; invoke the print macro

ror4: mov rax, [b64] ; data to shift

ror rax,4 ; shift

prt "ror rax,4 " ; invoke the print macro

shld4: mov rax, [b64] ; data to shift

mov rdx,0 ; register receiving bits

shld rdx,rax,8 ; shift

mov [raxsave],rax ; save, destroyed by function

mov [rdxsave],rdx ; save, destroyed by function

prt2 "shld rdx,rax,8"; invoke the print macro

shla: mov rax,[raxsave] ; restore, destroyed by function

mov rdx,[rdxsave] ; restore, destroyed by function

shl rax,8 ; finish double shift, both registers

prt2 "shl rax,8 "; invoke the print macro

shrd4: mov rax, [b64] ; data to shift

mov rdx,0 ; register receiving bits

shrd rdx,rax,8 ; shift

mov [raxsave],rax ; save, destroyed by function

mov [rdxsave],rdx ; save, destroyed by function

prt2 "shrd rdx,rax,8"; invoke the print macro

shra: mov rax,[raxsave] ; restore, destroyed by function

mov rdx,[rdxsave] ; restore, destroyed by function

shr rax,8 ; finish double shift, both registers

prt2 "shr rax,8 "; invoke the print macro

pop rbp ; restore stack

mov rax,0 ; exit code, 0=normal

ret ; main returns to operating system

First project is assigned.

You may want to wait until the next lecture and do HW3 before

starting the project. Code and debug your first Nasm program.

www.cs.umbc.edu/~squire/cs313_proj.shtml

See www.csee.umbc.edu/help/nasm/nasm_64.shtml for notes on using debugger.

A program that prints where its sections are allocated

(in virtual memory) is where_64.asm

My output, yours should be different, is

where_64.lst

where_64.out

where_64.dbg

; where_64.asm print addresses of sections

; Assemble: nasm -g -f elf64 -l where_64.lst where_64.asm

; Link: gcc -g3 -m64 -o where_64 where_64.o

; Run: ./where_64 > where_64.out

; Output: you need to run it, results on my computer:

; data a: at ??? waries with computer and software

; bss b: at ???

; rodata c: at ???

; code main: at ???

;

; to debug, typically after segfault

; gdb where_64

; run

; backtrace

; optionally: disassemble x/60x main

; end with q y

extern printf ; the C function, to be called

section .data ; Data section, initialized variables

a: db 0,1,2,3,4,5,6,7

fmt: db "data a: at %lX",10

db "bss b: at %lX",10

db "rodata c: at %lX",10

db "code main: at %lX",10,0

section .bss ; reserved storage, uninitialized

b: resq 8

section .rodata ; read only initialized storage

c: db 7,6,5,4,3,2,1,0

section .text ; Code section.

global main ; the standard gcc entry point

main: ; the program label for the entry point

push rbp

mov rbp,rsp

push rbx ; save callers registers

mov rdi,fmt ; pass address of fmt to printf

lea rsi,[a] ; using load effective address

lea rdx,[b] ; using load effective address

lea rcx,[c] ; using load effective address

lea r8,[main] ; using load effective address

mov rax,0 ; no float

call printf ; Call C function

mov rdi,fmt ; pass address of fmt to printf

mov rsi,a ; just loading address

mov rdx,b ; just loading address

mov rcx,c ; just loading address

mov r8,main ; just loading address

mov rax,0 ; no float

call printf ; Call C function

pop rbx ; restore callers registers

mov rsp,rbp

pop rbp

mov rax,0 ; normal, no error, return value

ret ; return

My output on gl.linux.umbc.edu is where_64.out (my notes added)

data a: at 6008CC .data start

bss b: at 600930 .bss start after .data

rodata c: at 400658 .rodata start after .text

code main: at 4004D0 .text start

data a: at 6008CC

bss b: at 600930

rodata c: at 400658

code main: at 4004D0

To run debugger and look at disassemble and memory dump

gdb where_64 > where_64.dbg

break main

run

disassemble

x/60x main

q

y

A small part of my output from debugger where_64.dbg

GNU gdb (GDB) Red Hat Enterprise Linux (7.2-83.el6)

...

(gdb) break main

Breakpoint 1 at 0x4004d4: file where_64.asm, line 37.

(gdb) run

Starting program: /afs/umbc.edu/users/s/q/squire/home/cs313/where_64

Breakpoint 1, main () at where_64.asm:37

37 push rbx ; save callers registers

Missing separate debuginfos, use: debuginfo-install glibc-2.12-1.166.el6_7.3.x86_64

(gdb) disassemble

Dump of assembler code for function main:

0x00000000004004d0 +0: push %rbp

0x00000000004004d1 +1: mov %rsp,%rbp

=> 0x00000000004004d4 +4: push %rbx

0x00000000004004d5 +5: movabs $0x6008d4,%rdi

0x00000000004004df +15: lea 0x6008cc,%rsi

0x00000000004004e7 +23: lea 0x600930,%rdx

0x00000000004004ef +31: lea 0x400658,%rcx

0x00000000004004f7 +39: lea 0x4004d0,%r8

0x00000000004004ff +47: movabs $0x0,%rax

0x0000000000400509 +57: callq 0x4003b8 printf@plt

0x000000000040050e +62: movabs $0x6008d4,%rdi

0x0000000000400518 +72: movabs $0x6008cc,%rsi

0x0000000000400522 +82: movabs $0x600930,%rdx

0x000000000040052c +92: movabs $0x400658,%rcx

0x0000000000400536 +102: movabs $0x4004d0,%r8

0x0000000000400540 +112: movabs $0x0,%rax

0x000000000040054a +122: callq 0x4003b8 printf@plt

0x000000000040054f +127: pop %rbx

0x0000000000400550 +128: mov %rbp,%rsp

0x0000000000400553 +131: pop %rbp

0x0000000000400554 +132: movabs $0x0,%rax

0x000000000040055e +142: retq

0x000000000040055f +143: nop

End of assembler dump.

(gdb) x/60x main

0x4004d0 main: 0xe5894855 0xd4bf4853 0x00006008 0x48000000

...

A debugging session is active.

Inferior 1 [process 23721] will be killed.

Quit anyway? (y or n)

Options that may allow you to debug

Typical assembly language programming, may just use registers,

or may keep most variables just in registers.

Storing variables in memory may be needed for debugging.

This example starts with a small C program,fib.c

then codes efficient assembly language,fib_64l.asm

Output, shows overflow fib_64l.out

then keeps variables in memory,fib_64m.asm

// fib.c same as computation as fib_64.asm

#include <stdio.h>

int main(int argc, char *argv[])

{

long int c = 95; // loop counter

long int a = 1; // current number, becomes next

long int b = 2; // next number, becomes sum a+b

long int d; // temp

printf("fibinachi numbers\n");

for(c=c; c!=0; c--)

{

printf("%21ld\n",a);

d = a;

a = b;

b = d+b;

}

}

implement fib.c using registers

; fib_64l.asm using 64 bit registers to implement fib.c

global main

extern printf

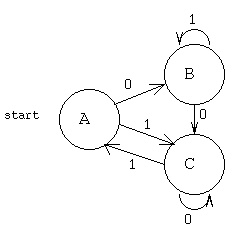

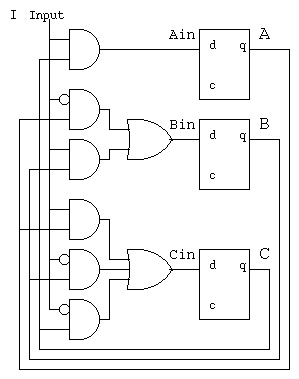

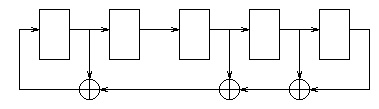

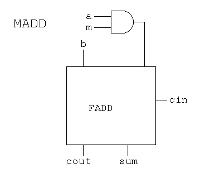

section .data