# High Electron Velocity Submicrometer AlN/GaN MOS-HEMTs on Freestanding GaN Substrates

David J. Meyer, *Member, IEEE*, David A. Deen, *Member, IEEE*, David F. Storm, Mario G. Ancona, *Member, IEEE*, D. Scott Katzer, *Member, IEEE*, Robert Bass, Jason A. Roussos, *Member, IEEE*, Brian P. Downey, Steven C. Binari, *Member, IEEE*, Theodosia Gougousi, Tanya Paskova, Edward A. Preble, and Keith R. Evans

Abstract—AlN/GaN heterostructures with 1700-cm<sup>2</sup>/V · s Hall mobility have been grown by molecular beam epitaxy on freestanding GaN substrates. Submicrometer gate-length  $(L_G)$  metal–oxide–semiconductor (MOS) high-electron-mobility transistors (HEMTs) fabricated from this material show excellent dc and RF performance.  $L_G = 100$  nm devices exhibited a drain current density of 1.5 A/mm, current gain cutoff frequency  $f_T$  of 165 GHz, a maximum frequency of oscillation  $f_{\rm max}$  of 171 GHz, and intrinsic average electron velocity  $v_e$  of  $1.5 \times 10^7$  cm/s. The 40-GHz load-pull measurements of  $L_G = 140$  nm devices showed 1-W/mm output power, with a 4.6-dB gain and 17% power-added efficiency. GaN substrates provide a way of achieving high mobility, high  $v_e$ , and high RF performance in AlN/GaN transistors.

*Index Terms*—Atomic layer deposition, AlN, GaN, highelectron-mobility transistors (HEMTs), HfO<sub>2</sub>, hydride vapor phase epitaxy (HVPE).

## I. INTRODUCTION

**R** ECENT research to increase the frequency performance of GaN high-electron-mobility transistors (HEMTs) has focused on aggressively scaling the device geometry. As GaN HEMT gate lengths  $L_G$  are reduced below 0.25  $\mu$ m, the demands of electrostatic control have led to the use of novel ultrathin barriers with higher Al mole fractions than conventional AlGaN alloys. For Ga-polar heterostructures, AlN is the thinnest pseudomorphic barrier material available that can induce (via polarization and conduction band discontinuity) a 2-D electron gas (2DEG) density suitable for transistor use in GaN [1]. Early reports of RF devices based on the AlN/GaN heterostructure showed the potential of scaling the barrier

Manuscript received October 23, 2012; revised November 8, 2012; accepted November 12, 2012. This work was supported by the Office of Naval Research with funding from Dr. P. Maki. The work at the University of Maryland Baltimore County was supported in part by the National Science Foundation under Grant DMR 0846445. The review of this letter was arranged by Editor J. A. del Alamo.

D. J. Meyer, D. F. Storm, M. G. Ancona, D. S. Katzer, R. Bass, J. A. Roussos, B. P. Downey, and S. C. Binari are with the U.S. Naval Research Laboratory, Washington, DC 20375 USA (e-mail: david.meyer@nrl.navy.mil).

D. A. Deen was with the U.S. Naval Research Laboratory, Washington, DC 20375 USA. He is now with the Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN 55455 USA (e-mail: dadeen@umn.edu).

T. Gougousi is with the Department of Physics, University of Maryland-Baltimore County, Baltimore, MD 21250 USA.

T. Paskova was with Kyma Technologies, Raleigh, NC 27617 USA. She is now with the Department of Material Science and Engineering, North Carolina State University, Raleigh, NC 27695 USA.

E. A. Preble and K. R. Evans are with Kyma Technologies, Raleigh, NC 27617 USA.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2012.2228463

1

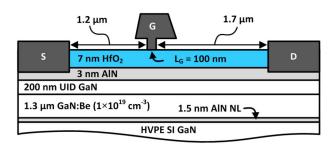

Fig. 1. Cross-sectional schematic of an  $L_G=100~\mathrm{nm}$  AlN/GaN MOS-HEMT.

thickness by demonstrating current gain cutoff frequency  $f_T$  values in the 50- to 110-GHz range [2], [3]. More recently, dramatic reduction in source–drain spacing  $L_{SD}$  down to 100 nm, selective regrowth of n<sup>+</sup> GaN source and drain regions by molecular beam epitaxy (MBE), and AlGaN back barriers have been used to demonstrate the highest combination of  $f_T = 310$  GHz and the maximum frequency of oscillation  $f_{\text{max}}$  of 364 GHz for depletion-mode GaN HEMTs to date [4].

While device engineering can be used to minimize certain electron delay components such as parasitic and channel charging, the primary constituents of total electron delay  $(2\pi f_T)^{-1}$  are typically the drain delay and intrinsic gate transit times, which are inversely proportional to the average electron velocity  $v_e$  in their respective regions [4], [5]. The goal of this study was to determine whether higher  $v_e$  can be achieved with the use of hydride vapor phase epitaxy (HVPE)-grown freestanding GaN as a substrate for AlN/GaN HEMT device epitaxy. Since epitaxial layers can be grown with a low dislocation density  $(< 10^7 \text{ cm}^{-2})$  on HVPE GaN [6], this substrate offers a lattice- and thermal-expansionmatched platform for heterostructure growth that has potential advantages over previously examined substrates such as Si [7], sapphire [1]–[3], [8], [9], and SiC [4], [5], [9]–[12]. To evaluate the dc and RF electrical performance of this material, we fabricated and tested submicrometer T-gate AlN/GaN MOS-HEMT devices, as schematically shown in Fig. 1.

### **II. EXPERIMENT**

The HEMT structure was grown by RF-plasma-assisted MBE on a 1 cm  $\times$  1 cm freestanding HVPE-grown GaN semi-insulating substrate at 650 °C. Following a 60-s surface nitridation of the GaN substrate, growth began with a 1.5-nm-thick AlN nucleation layer [13]. A 1.3- $\mu$ m-thick GaN layer was then grown with beryllium doping used to suppress buffer leakage current [14]. Finally, a 200-nm-thick unintentionally doped (UID) GaN buffer layer was grown and capped with a

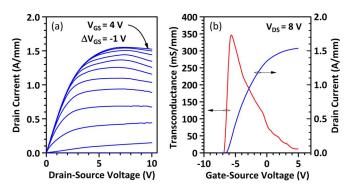

Fig. 2. (a) Drain and (b) transfer curves for an  $L_G = 100$  nm AlN/GaN device.

3-nm AlN barrier layer. The GaN layers were grown in a metalrich regime at a gallium/active nitrogen flux ratio of 1.4. The AlN layers were grown with an aluminum/active nitrogen flux ratio  $\approx 1$ .

The device fabrication began with a Ti/Al/Ni/Au (30 nm/ 200 nm/40 nm/20 nm) ohmic-first process that used a premetallization etch [15] to recess the contact metal prior to annealing at 800 °C. After annealing, the ohmic contact resistance was measured to be 0.3–0.4  $\Omega$ -mm using circular transfer length method patterns. Following standard Cl<sub>2</sub>/BCl<sub>3</sub>-based dry etch mesa isolation, a 7-nm HfO<sub>2</sub> gate insulator was blanket deposited using tetrakis (ethylmethyl) amino hafnium (TEMAHf) and water at 250 °C by atomic layer deposition. Submicrometer Ni/Au (20 nm/300 nm) T-shaped gates were defined by electron-beam lithography. The device  $L_{SD}$  was 3  $\mu$ m, gate width  $W_G$ was 2 × 75  $\mu$ m, and  $L_G$  were 0.1, 0.14, and 2  $\mu$ m. For the submicrometer T-gates, the gate head length was 0.5  $\mu$ m. All dimensions were measured by scanning electron microscopy.

### **III. RESULTS AND DISCUSSION**

Room-temperature on-wafer Hall effect measurements were taken before and after HfO<sub>2</sub> deposition to determine low-field transport properties. Prior to oxide deposition, the average sheet resistance  $R_{\rm sh}$  was 194  $\Omega/{\rm sq}$  with a 2DEG density of  $n_s = 1.9 \times 10^{13}$  cm<sup>-2</sup> and mobility of 1700 cm<sup>2</sup>/V · s. Following oxide deposition,  $R_{\rm sh}$  dropped to 164  $\Omega/{\rm sq}$  with an associated increase in  $n_s = 2.4 \times 10^{13}$  cm<sup>-2</sup> and a slight reduction in mobility to 1600 cm<sup>2</sup>/V · s. With the 2DEG  $n_s$  well in excess of  $10^{13}$  cm<sup>-2</sup> in the access regions, we suspect that there is sufficient Debye screening of charged dislocations and that the resulting mobility is therefore limited by polar optical phonon scattering and interfacial roughness [1].

DC electrical characteristics for an  $L_G = 100$  nm device are shown in Fig. 2. An OFF-state breakdown voltage of 35 V was measured with  $V_{GS} = -7$  V and 1 mA/mm of drain leakage current. Fig. 2(b) shows the transfer characteristics for the 100-nm device with a maximum current density of 1.5 A/mm, a threshold voltage of approximately -6.3 V, and a subthreshold swing of 162 mV/dec (not shown). Minimal hysteresis (< 100 mV) was observed when the transfer curve was immediately swept in the reverse direction after an initial trace. The peak transconductance  $g_{m,\max}$  was measured to be 347 mS/mm. Intrinsic  $g_{m,\max}$  was estimated to be 419 mS/mm when the voltage drops across  $R_s$  were accounted for. The sharp asymmetric shape of the transconductance curve is not fully understood at this time but is likely related to the dynamic

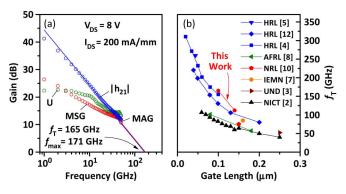

Fig. 3. (a) Pad deembedded small-signal characteristics of an AlN/GaN device with  $L_G = 100$  nm. (b)  $f_T$  results from this study ( $L_G = 100$  and 140 nm) compared with other previously reported AlN/GaN HEMT small-signal  $f_T$ .

**Equivalent Circuit Model Parameters**

| $L_{\rm G} = 100  \rm nm$              | Bias Conditions                           |  |

|----------------------------------------|-------------------------------------------|--|

| $W_{\rm G} = 2 \times 75 \ \mu { m m}$ | $V_{\rm DS} = 8 V / V_{\rm GS} = -5.25 V$ |  |

| $g_{\rm m}({\rm mS})$                  | 75.2                                      |  |

| $g_{\rm d}({\rm mS})$                  | 5.1                                       |  |

| $C_{\rm gs}({ m fF})$                  | 49.3                                      |  |

| $C_{\rm gd}({\rm fF})$                 | 14.0                                      |  |

| $R_{ m i}\left(\Omega ight)$           | 1                                         |  |

| $R_{ m g}\left(\Omega ight)$           | 5                                         |  |

| $R_{\rm s}(\Omega)$                    | 4                                         |  |

| $R_{\rm d}(\Omega)$                    | 4                                         |  |

**Calculated Values**

| Delay Component        | Value (ps) | Figures of Merit                |                    |

|------------------------|------------|---------------------------------|--------------------|

| Parasitic charging     | 0.11       | $f_{\rm T,model}$ (GHz)         | 161                |

| Channel charging       | 0.03       | $f_{\rm T,measured}$ (GHz)      | 165                |

| Drain delay            | 0.19       | $f_{\rm max,model}$ (GHz)       | 176                |

| Intrinsic gate transit | 0.66       | fmax, measured (GHz)            | 171                |

| Total electron delay   | 0.99       | Intrinsic v <sub>e</sub> (cm/s) | $1.53 \times 10^7$ |

Fig. 4. Equivalent circuit modeling results and extracted parameters of the  $L_G = 100$  nm AlN/GaN device in Fig. 3(a).

access resistance [16] or the carrier energy clamping due to optical phonon emission [17].

Small-signal characteristics for a MOS-HEMT with  $L_G =$ 100 nm, with pad parasitics deembedded, are shown in Fig. 3(a).  $f_T = 165$  GHz and  $f_{max} = 171$  GHz were determined by -20-dB/dec extrapolation of the small-signal current gain,  $|h_{21}|$ , and the maximum available gain (MAG), respectively. Prior to deembedding of probe pad parasitics (determined by cold field-effect transistor method [18]), the extrinsic  $f_T/f_{\rm max}$  were 120 GHz/170 GHz for the  $L_G = 100$  nm device in Fig. 3(a). Pad deembedded  $f_T/f_{\rm max}$  values of 112 GHz/ 134 GHz and 10 GHz/27 GHz were extracted for the 140 nm and 2- $\mu$ m-L<sub>G</sub> devices, respectively. Fig. 3(b) compares the small-signal  $f_T$  results from this study to literature values for AlN/GaN HEMTs. Despite having a relatively long  $L_{SD}$  = 3  $\mu$ m, we observe that the  $f_T$  values from the devices in this study are in line with the highest reported values at coincident  $L_G$ . To investigate whether the improved small-signal performance of our devices was due to reduced parasitic effects or shorter intrinsic delay, small-signal modeling of the measured S-parameter data was conducted.

Fig. 4 summarizes results of small-signal equivalent circuit model fitting to the measured S-parameters of the  $L_G = 100$  nm MOS-HEMT in Fig. 3(a). [19]. Of the delays, the parasitic charging [defined as  $C_{gd} \cdot (R_s + R_d)$ ] and the channel charging [calculated as  $(g_{ds}/g_m) \cdot (C_{gd} + C_{gs}) \cdot (R_s + R_d)$ ]

MEYER et al.: HIGH ELECTRON VELOCITY SUBMICROMETER AIN/GaN MOS-HEMTs

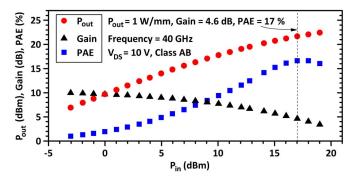

Fig. 5. The 40-GHz power sweep of an  $L_G = 140$  nm AlN/GaN device.

are relatively small percentages of the total delay (~11% and 4%, respectively). The drain delay, i.e.,  $C_{ad}/g_m$ , is more substantial (19%) and potentially arises from the large drain bias (8 V) causing an expansion of the drain-side depletion region. The largest contributor to the total delay, according to our modeling, is the intrinsic gate transit time, i.e.,  $C_{qs}/g_m$ . By dividing  $L_G$  by the intrinsic gate transit time, intrinsic  $v_e$ is calculated to be  $1.53 \times 10^7$  cm/s for the 100-nm device. An identical analysis of a 140-nm device found the intrinsic  $v_e$  to be  $1.49 \times 10^7$  cm/s, with intrinsic gate transit and total delay times of 0.94 and 1.36 ps, respectively. These values of  $v_e$ are among the highest reported for AlN/GaN HEMTs, which range from  $0.8-1.5 \times 10^7$  cm/s [2], [4], [12]. In the case of the highest reported  $v_e$  [4], velocity enhancement was achieved by laterally scaling the device to increase the lateral electric field across the intrinsic device. We speculate that the elevated velocity in this study is *not* due to velocity enhancement but, instead, is a result of using epitaxial material grown on HVPE GaN, where low dislocation densities in the low-field portion of the intrinsic device result in minimal mobility degradation when the gate is biased for peak  $f_T$  (and  $n_{\rm sh}$  is reduced <  $1 \times 10^{13}$  cm<sup>-2</sup>) [20]. In higher dislocation density material, the depletion of the 2DEG underneath the gate metal, when biased for peak  $f_T$ , could significantly reduce the Debye screening of charged dislocations and render electron transport susceptible to Coulombic scattering and, consequently, lower intrinsic  $v_e$ .

To evaluate the large-signal potential of these devices, 500-ns pulsed gate lag measurements were performed at quiescent biases of  $V_{DS} = 10$  V and  $V_{GS} = -7$  V and showed gate lag ratios (pulsed  $I_{DSS}/dc I_{DSS}$ ) of 0.8–1.0 for all devices in this study. Subsequent on-wafer 40-GHz load-pull measurements taken on a 140-nm device biased in class AB ( $V_{DS} = 10$  V, and  $V_{GS} = -4.5$  V) gave the results shown in Fig. 5. At the peak power-added efficiency (PAE) of 17%, the gain was 4.6 dB, and the output power density was 1 W/mm. This result shows the potential for AlN/GaN HEMTs to produce millimeter-wavelength power.

#### **IV. CONCLUSION**

To the best of our knowledge, this is the first demonstration of an AlN/GaN MOS-HEMT on freestanding GaN. Epitaxial growth on HVPE GaN has been shown to yield submicrometer devices with excellent dc and RF performance. Reflective of the material quality, a high value of intrinsic average electron velocity ( $v_e = 1.5 \times 10^7$  cm/s) was extracted for these devices.

#### REFERENCES

- Y. Cao and D. Jena, "High-mobility window for two-dimensional electron gases at ultrathin AlN/GaN heterojunctions," *Appl. Phys. Lett.*, vol. 90, no. 18, p. 182 112-3, Apr. 2007.

- [2] M. Higashiwaki, T. Mimura, and T. Matsui, "AlN/GaN insulated-gate HFETs using Cat-CVD SiN," *IEEE Electron Device Lett.*, vol. 27, no. 9, pp. 719–721, Sep. 2006.

- [3] T. Zimmermann, D. Deen, Y. Cao, J. Simon, P. Fay, D. Jena, and H. G. Xing, "AlN/GaN insulated-gate HEMTs with 2.3 A/mm output current and 480 mS/mm transconductance," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 661–664, Jul. 2008.

- [4] K. Shinohara, D. Regan, A. Corrion, D. Brown, S. Burnham, P. J. Willadsen, I. Alvarado-Rodriguez, M. Cunningham, C. Butler, A. Schmitz, S. Kim, B. Holden, D. Chang, V. Lee, A. Ohoka, P. M. Asbeck, and M. Micovic, "Deeply-scaled self-aligned-gate GaN DH-HEMTs with ultrahigh cutoff frequency," in *IEDM Tech. Dig.*, 2011, pp. 453–456.

- [5] K. Shinohara, D. Regan, I. Milosavljevic, A. L. Corrion, D. F. Brown, P. J. Willadsen, C. Butler, A. Schmitz, S. Kim, V. Lee, A. Ohoka, P. M. Asbeck, and M. Micovic, "Electron velocity enhancement in laterally scaled GaN DH-HEMTs with f<sub>T</sub> of 260 GHz," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1074–1076, Aug. 2011.

- [6] D. F. Storm, D. S. Katzer, J. A. Roussos, J. A. Mittereder, R. Bass, S. C. Binari, L. Zhou, D. J. Smith, D. Hanser, E. A. Preble, and K. R. Evans, "Microwave performance and structural characterization of MBEgrown AlGaN/GaN HEMTs on low dislocation density GaN substrates," *J. Cryst. Growth*, vol. 305, no. 2, pp. 340–345, Jul. 2007.

- [7] F. Medjdoub, M. Zegaoui, N. Waldhoff, B. Grimbert, N. Rolland, and P.-A. Rolland, "Above 600 mS/mm transconductance with 2.3 A/mm drain current density AlN/GaN high-electron-mobility transistors grown on silicon," *Appl. Phys. Exp.*, vol. 4, p. 064106, Jun. 2011.

- [8] K. D. Chabak, D. E. Walker, M. R. Johnson, A. Crespo, A. M. Dabiran, D. J. Smith, A. M. Wowchak, S. K. Tetlak, M. Kossler, J. K. Gillespie, R. C. Fitch, and M. Trejo, "High-performance AlN/GaN HEMTs on sapphire substrate with an oxidized gate insulator," *IEEE Electron Device Lett.*, vol. 32, no. 12, pp. 1677–1679, Dec. 2011.

- [9] A. M. Dabiran, A. M. Wowchak, A. Osinsky, J. Xie, B. Hertog, B. Cui, D. C. Look, and P. P. Chow, "Very high channel conductivity in low-defect AlN/GaN high electron mobility transistor structures," *Appl. Phys. Lett.*, vol. 93, no. 8, p. 082 111-3, Aug. 2008.

- [10] D. A. Deen, S. C. Binari, D. F. Storm, D. S. Katzer, J. A. Roussos, J. C. Hackley, and T. Gougousi, "AIN/GaN insulated gate HEMTs with HfO<sub>2</sub> gate dielectric," *Electron. Lett.*, vol. 45, no. 8, pp. 423–424, Apr. 2009.

- [11] D. A. Deen, D. F. Storm, R. Bass, D. J. Meyer, D. S. Katzer, S. C. Binari, J. W. Lacis, and T. Gougousi, "Atomic layer deposited Ta<sub>2</sub>O<sub>5</sub> gate insulation for enhancing breakdown voltage of AlN/GaN high electron mobility transistors," *Appl. Phys. Lett.*, vol. 98, no. 2, p. 023506-3, Jan. 2011.

- [12] K. Shinohara, A. Corrion, D. Regan, I. Milosavljevic, D. Brown, S. Burnham, P. J. Willadsen, C. Butler, A. Schmitz, D. Wheeler, A. Fung, and M. Micovic, "220 GHz f<sub>T</sub> and 400 GHz f<sub>max</sub> in 40-nm GaN DH-HEMTs with regrown ohmic," in *Proc. IEDM Tech. Dig.*, 2010, pp. 672–675.

- [13] Y. Cao, T. Zimmermann, H. Xing, and D. Jena, "Polarization-engineered removal of buffer leakage for GaN transistors," *Appl. Phys. Lett.*, vol. 96, no. 4, p. 042102-3, Jan. 2010.

- [14] D. F. Storm, D. S. Katzer, D. A. Deen, R. Bass, D. J. Meyer, J. A. Roussos, S. C. Binari, T. Paskova, E. A. Preble, and K. R. Evans, "Proximity effects of beryllium-doped GaN buffer layers on the electronic properties of epitaxial AlGaN/GaN heterostructures," *Solid State Electron.*, vol. 54, no. 11, pp. 1470–1473, Nov. 2010.

- [15] D. A. Deen, D. F. Storm, D. S. Katzer, D. J. Meyer, and S. C. Binari, "Dependence of ohmic contact resistance on barrier thickness of AlN/GaN HEMT structures," *Solid State Electron.*, vol. 54, no. 6, pp. 613–615, Jun. 2010.

- [16] T. Palacios, S. Rajan, A. Chakraborty, S. Heikman, S. Keller, S. P. DenBaars, and U. K. Mishra, "Influence of the dynamic access resistance in the  $g_m$  and  $f_T$  linearity of AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2117–2123, Oct. 2005.

- [17] T. Fang, R. Wang, H. Xing, S. Rajan, and D. Jena, "Effect of optical phonon scattering on the performance of GaN transistors," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 709–711, May 2012.

- [18] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 7, pp. 1151–1159, Jul. 1988.

- [19] P. J. Tasker and B. Hughes, "Importance of source and drain resistance to the maximum  $f_T$  of millimeter-wave MODFETs," *IEEE Electron Device Lett.*, vol. 10, no. 7, pp. 291–293, Jul. 1989.

- [20] D. Jena, A. C. Gossard, and U. K. Mishra, "Dislocation scattering in a two-dimensional electron gas," *Appl. Phys. Lett.*, vol. 76, no. 13, pp. 1707–1709, Mar. 2000.