Combinational logic accepts inputs and produces output after some delay. Truth table = circuit diagram = VHDL code inputs | outputs ABC S Co unoptimized VHDL from truth table 0 0 0 0 0 1 0 S <= (not A and not B and C) or 0 0 1 1 0 (not A and В and not C) or 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 ( A and not B and Not C) or A and B and ( C) after 1 ns; 101 0 1 0 1 C<sub>o</sub> <= (not A and B and ( A and not B and C) or 1 1 0 1 1 1 C) or 11 A and B and not C) or ( A and B and C) after 1 ns;

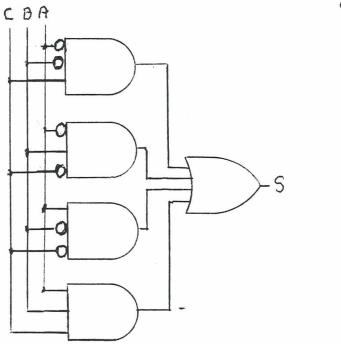

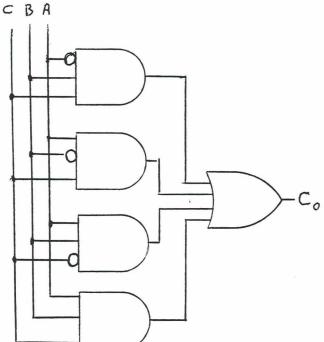

unoptimized circuit diagram from truth table

3-10

Sequential circuits have storage elements (registers of flip flops)

Combinational circuits MUST NOT HAVE LOOPS !

Any feedback loop must have a clocked storage element otherwise is may become locked in one state or may become an oscillator.

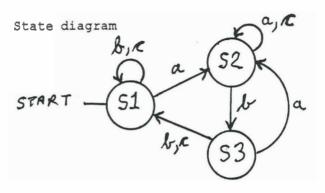

State transition\_table = State diagram = Circuit diagram = VHDL code

State transition table

| state | 1 | inputs |    |    |

|-------|---|--------|----|----|

|       | 1 | a      | b  | С  |

|       | + |        |    |    |

| S1    | 1 | S2     | S1 | S1 |

| S2    | 1 | S2     | S3 | S2 |

| S3    | 1 | S2     | S1 | S1 |

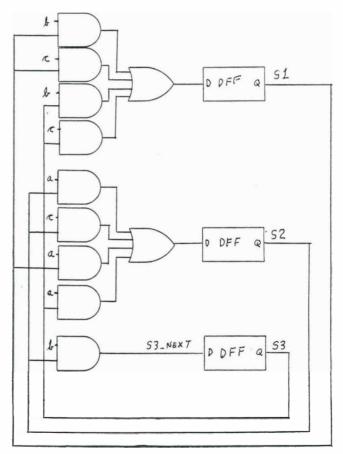

Circuit diagram (unoptimized)

unoptimized VHDL code

S1\_next <= (S1 and b) or (S1 and c) or (S3 and b) or (S3 and c) after 1 ns; S2\_next <= (S2 and a) or (S2 and c) or (S1 and a) or (S3 and a) after 1 ns; S3\_next <= (S2 and b) after 1 ns; S1\_dff: entity work.dff port map(S1\_next, clk, '1', start, S1); S2\_dff: entity work.dff port map(S2\_next, clk, start, '1', S2); S3\_dff: entity work.dff port map(S3\_next, clk, start, '1', S3);