## Microcontact patterning of ruthenium gate electrodes by selective area atomic layer deposition

K. J. Park, <sup>a)</sup> J. M. Doub, T. Gougousi, and G. N. Parsons Department of Chemical and Biomolecular Engineering, North Carolina State University, Raleigh, North Carolina 27695

(Received 21 July 2004; accepted 16 November 2004; published online 26 January 2005)

Patterned octadecyltrichlorosilane monolayers are used to inhibit film nucleation, enabling selective area atomic layer deposition (ALD) of ruthenium on  $SiO_2$  and  $HfO_2$  surfaces using bis-(cyclopentadienyl)ruthenium and oxygen. X-ray photoelectron spectroscopy indicated that OTS could deactivate film growth on thermal silicon oxide and hafnium oxide surfaces. The growth rate of ALD Ru is similar on various starting surfaces, but the growth initiation differed substantially. Metal-oxide-semiconductor capacitors were fabricated directly using the selective-area process. Capacitance measurements indicate the effective work function of ALD Ru is  $4.84 \pm 0.1$  eV on  $SiO_2$ , and the effective work function is reduced on  $HfO_2/SiO_2$  layers. © 2005 American Institute of Physics. [DOI: 10.1063/1.1852079]

Improved control of interface reactions during thin film processing is critical for advanced electronic and optical devices. Ruthenium is of interest for advanced metal/oxide/semiconductor (MOS) transistor gate electrodes to reduce polysilicon depletion effects and as nucleation layer for copper interconnect layers. Ruthenium is considered a viable candidate for *p*-type MOS devices because it has a vacuum work function near the conduction band edge of silicon, good thermal stability, and low resistivity of the oxidation phase. <sup>2</sup>

Microcontact-printed organic monolayer resists have previously been used for selective area atomic layer deposition (ALD) of oxides<sup>3–5</sup> and for chemical vapor deposition (CVD) of metals.<sup>6</sup> A previous report demonstrates selective area digital CVD Ru using patterned photoresist.<sup>7</sup> In this work, selective deposition of Ru is demonstrated using contact printed self-assembled monolayer resists by ALD processing. Also in this work, spectroscopic characterization is used to demonstrate selectivity, and the effect of processing on the monolayer structure is analyzed. Selective deposition enables direct formation of Ru/HfO<sub>2</sub>(SiO<sub>2</sub>)/Si capacitor stacks, and the effective work function of ALD Ru is characterized on HfO2 and SiO2 dielectrics. A key problem for metals in CMOS is methodology to enable integration of two different metal work functions. Techniques to integrate two different metals in nanoscale device fabrication include selective modification of a metal, for example by interdiffusion<sup>8,9</sup> or by silicide formation, <sup>10</sup> or by metal alloy formation. <sup>11</sup> We suggest here that selective area ALD is a possible alternate route to dual-metal gate integration.

ALD Ru was carried out in a home-built hot-wall quartz tube reactor using RuCp<sub>2</sub> [bis-(cyclopentadienyl)ruthenium] as a precursor and dry oxygen. RuCp<sub>2</sub> is solid at room temperature with vapor pressure of  $\sim 10$  mTorr at the bubbler temperature of 80 °C. To prepare substrates, silicon surfaces were oxidized by wet chemical treatment (BakerClean® JTB-100), followed by buffered HF acid dip, deionized water rinse, and N<sub>2</sub> flow dry. Silicon was either directly oxidized to form SiO<sub>2</sub>, (900 °C in air) or coated with thin Hf

films by sputtering, followed by thermal oxidation. For example, the Hf based films with equivalent oxide thickness (EOT) of 30 Å consisted of 11 Å of sputtered hafnium followed by oxidized in N<sub>2</sub> (with ~20 ppm O<sub>2</sub>) at 600 °C for 1 min. <sup>12</sup> These conditions likely resulted in growth of HfO<sub>2</sub> with some interfacial HfSiO<sub>x</sub> and/or SiO<sub>2</sub>. The samples are referred to here as HfO<sub>2</sub>/SiO<sub>2</sub> films.

To prepare the patterned organic monolayer an elastomeric stamp was made of polydimethylsiloxane (PDMS) solution and a curing agent. The mold patterns for the PDMS stamps were micron-scale line/space photoresist and metallic dots made by physical vapor deposition of aluminum through a shadow mask. A solution of OTS (octadecyltrichlorosilane) in dry hexane (10 mM) was used as the "ink." The OTS solution was applied to the PDMS stamp by spin coating, and the inked stamp was dried in nitrogen flow for 30 s. The stamp was then brought into contact with the clean substrate and held in place for 30-60 s. The resulting OTS films were characterized by water contact angle analysis, scanning force microscopy, and x-ray photoelectron spectroscopy (XPS). For some measurements, OTS was also deposited by directly exposing the oxidized silicon to its solution at room temperature. Resulting films showed a static contact angle with water to be between <90 and 110°, consistent with a range of film quality, from relatively poorly packed (<90°), to highly packed (110°) films. 13,14 Films with contact angle ≥90° show similar results in inhibiting deposition. After exposure to 300 cycles of Ru ALD, the OTS monolayers generally showed reduced contact angle (<80°), indicating monolayer degradation. The results suggest that Ru nucleation is not as sensitive to quality of the monolayer surface as observed for Hf or Zr oxide 15 and Ti based<sup>13</sup> film deposition. This may be due to the higher oxygen affinity of Hf, Zr, and Ti where these metals are more likely to penetrate the monolayer and react with oxide present at the Si/monolayer interface.

The OTS-patterned substrates were rinsed in hexane and deionized water, then dried with nitrogen flow before being loaded into the ALD reactor. The ALD chamber was evacuated to  $5 \times 10^{-6}$  Torr, and the precursor and oxidant gases were introduced into the reactor in separate pulses (3 and 6 s,

a) Electronic mail: kjpark@ncsu.edu

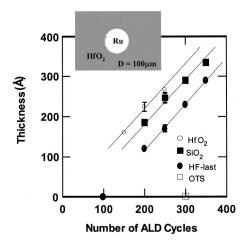

FIG. 1. Ruthenium film thickness vs number of ALD cycles as deposited on  $HfO_2$ ,  $SiO_2$ , and Si-H (HF-last) surfaces, compared to deposition on OTS covered substrate. The data point at zero thickness for growth on Si-H is determined from visual inspection. The data point at zero thickness for growth on OTS is determined from XPS. Visual inspection shows clear selectivity on OTS for all conditions studied (up to 300 cycles). The error bar for each substrate represents typical measurement error ( $\pm 5\%$ ) of profilometer. The inset shows an optical image of a selectively deposited Ru (100  $\mu$ m diameter) metal on  $HfO_2$ .

respectively) with a 20 s Ar purge between each reactant. Argon was also used as a carrier gas for the RuCp<sub>2</sub> pulse. During the deposition, the total gas flow rate was constant at 100 sccm, and the chamber was dynamically pumped to maintain pressure at 1.2 Torr. Under these conditions, self limiting growth was observed at temperatures between  $\sim 310^{\circ}$  and 350 °C corresponding to  $\sim 1$  Å per deposition cycle, which is larger that 0.5 Å/cycle reported previously for Ru ALD. <sup>16</sup> This difference is under investigation. The resulting Ru films were characterized by surface profilometry to determine thickness, and XPS was used to determine the film chemical composition. Capacitance versus voltage (C-V) was measured using an HP 4284A LCR meter at 1 MHz using p-type silicon substrates with doping levels of  $1.5 \times 10^{18}$  cm<sup>-3</sup>.

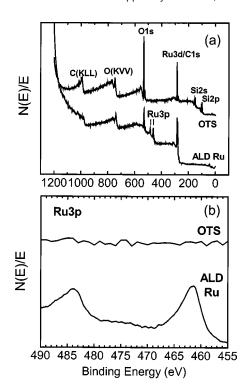

Figure 1 shows Ru film thickness versus number of ALD cycles for deposition on HfO<sub>2</sub>/SiO<sub>2</sub>, SiO<sub>2</sub>, and hydrogenterminated silicon (HF last) surfaces. For deposition on the Si–H surface, no film was observed by eye after 100 cycles for the conditions used. Also, on the OTS surface, no film was observed by XPS (vide infra) for up to 300 cycles studied. The inset in Fig. 1 is an optical image of a selectively deposited Ru capacitor on HfO2/SiO2 using the OTS monolayer resist. The deposited thickness per cycle was similar on SiO<sub>2</sub>, HfO<sub>2</sub>/SiO<sub>2</sub>, and Si–H, but the intercepts show different values, consistent with different incubation times for growth on these surfaces. However, details of growth incubation require more investigation of thin (<100 Å) layer growth. <sup>17</sup>Figures 2(a) and 2(b) show XPS spectra after 150 cycles of selective ALD Ru at 325 °C on clean SiO2 and on SiO<sub>2</sub> covered with microcontact-stamped OTS. Figure 2(b) shows that the Ru 3p peaks are not observed on the OTS covered regions after ALD, indicating good selectivity to Ru growth with this monolayer surface (static contact angle for this sample was 92° before Ru deposition). The measured Ru  $3p^{1/2}$  and  $3p^{3/2}$  peak positions at 484 and 462 eV, and the width of the peaks are consistent with the presence of several Ru oxidation states from elemental Ru to mildly oxi-

FIG. 2. (a) Survey scan, and (b) Ru 3p region from XPS analysis of a SiO<sub>2</sub> partially covered with OTS after 150 Ru ALD cycles at 325 °C; OTS: region with OTS covered, ALD Ru: Ru covered after on HfO<sub>2</sub> and SiO<sub>2</sub> compared to deposition on OTS covered substrate.

dized  $RuO_x$ . Presence of  $RuO_x$  is confirmed by the existence of the O 1s peak, although it is possible that most of the O in confined to the surface. Because of overlap of C 1s and Ru 3d peaks, it is difficult to calibrate the XP spectrum energy scale to compensate for surface charge. The spectrum from the Ru film shows a small signal from the Si substrate peak at 98.7 eV, close to the expected value of 99.3 eV.

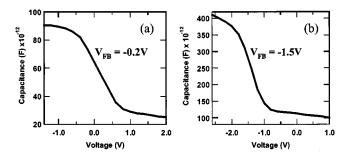

Figure 3(a) shows C-V characteristics of capacitors formed using selective area Ru deposition. For comparison, some capacitors [shown in Fig. 3(b)] were formed using blanket Ru followed by sputtered Al through a shadow mask and Ru dry etching. Before measurement, all capacitors received a post-metal anneal consisting of  $N_2:H_2=10:1$  at 400 °C for 30 min. The C-V behavior of the selective ALD Ru capacitor shows a flatband voltage ( $V_{\rm FB}$ ) of -0.2 V and equivalent oxide thickness of 30 Å as determined using the Hauser C-V fitting procedure. For the sputtered Al/ALD Ru capacitor,  $V_{\rm FB}$  is -1.5 V, consistent with a larger concentration of positive fixed charge in the dielectric induced by the Al sputter process that is not completely removed by the post-metal anneal.

with of the peaks are consistent with the presence of several Ru oxidation states from elemental Ru to mildly oxi-Downloaded 26 Jan 2005 to 130.85.162.193. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

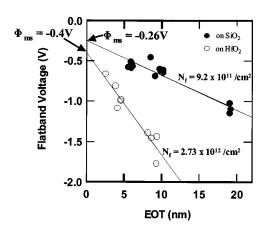

FIG. 4.  $V_{\rm FB}$  vs EOT for Ru/SiO<sub>2</sub>/Si and Ru/HfO<sub>2</sub>/Si capacitors. Quality of fittings (R): 0.9, the doping density of p-type Si:  $1.5 \times 10^{18}/{\rm cm}^3$ ,  $\phi_{\rm ms}$ : the work function difference between metal and silicon substrate.

A key question for advanced gate metals is the effective work function in a capacitor structure. The C-V curves were analyzed for a range of dielectric film thickness, and the results of  $V_{\rm FB}$  vs EOT are shown in Fig. 4. For the HfO<sub>2</sub>/ SiO<sub>2</sub> samples, determination of the effective work function  $(\phi_{\rm eff})$  from C-V data must consider the effect of charge at the SiO<sub>2</sub>/Si interface, as well as charge at any internal interface in the dielectric stack.<sup>20</sup> The data presented in Fig. 4 are not sufficient to unambiguously differentiate these interface charge densities, but the linear fit indicates that the bulk charge is relatively small in these films. For the case of Ru on SiO<sub>2</sub>, the intercept  $\phi_{\rm ms} = \phi_{\rm eff} - \phi_s$  where  $\phi_s$  is the semiconductor work function. In this case,  $\phi_{\rm eff}$  is determined to be 4.84±0.1 eV. The slope shows a high positive charge density at the Si/SiO2 interface. The more negative intercept for Ru on  $HfO_2/SiO_2$  is suggests a somewhat smaller  $\phi_{eff}$  at the (HfO<sub>2</sub>)/Ru interface, which is consistent with a different interface dipole due to differences in dielectric screening and charge neutrality levels in SiO<sub>2</sub> and HfO<sub>2</sub>. <sup>21,22</sup> For the Ru films reported here, Auger analysis indicates O/Ru ratio of  $\sim$ 3% and resistivity values ranged from 35 to 20  $\mu\Omega$  cm. An effective work function of 5.1 eV has been reported for CVD Ru on HfO2, where the Ru contains a higher concentration of oxygen.

Another problem with metal gate integration in complementary MOS technology is the potential need for two different metal gate materials for adjacent *n*- and *p*-type MOS

transistors. Processes that can selectively place one metal on a predetermined area of a substrate may provide a possible route to dual metal gate processing, to eliminate the need for a potentially damaging metal etch step. Alternate passivating approaches, beyond the OTS monolayer demonstrated here, would be helpful to further simplify processing requirements.

The authors gratefully acknowledge support from SE-MATECH and the Semiconductor Research Corporation (SRC) under the Front End Processing Research Center, and support from NSF under CTS - 0072784.

<sup>1</sup>H. Kim, J. Vac. Sci. Technol. B **21**, 2231 (2003).

<sup>2</sup>H. Zhong, G. Heuss, and V. Misra, IEEE Electron Device Lett. **21**, 593 (2000).

<sup>3</sup>M. Yan, Y. Koide, J. R. Babcock, P. R. Markworth, J. A. Belot, T. J. Marks, and R. P. H. Chang, Appl. Phys. Lett. **79**, 1709 (2001).

<sup>4</sup>R. Chen, H. Kim, P. C. McIntyre, and S. F. Bent, Appl. Phys. Lett. **84**, 4017 (2004).

<sup>5</sup>M. H. Park, Y. J. Jang, H. M. Sung-Suh, and M. M. Sung, Langmuir 20, 2257 (2004).

<sup>6</sup>N. L. Jeon, W. Lin, M. K. Erhard, G. S. Girolami, and R. G. Nuzzo, Langmuir **13**, 3833 (1997).

<sup>7</sup>S. K. Dey, J. Goswami, D. Gu, H. Waard, S. Marcus, and C. Werkhoven, Appl. Phys. Lett. **84**, 1606 (2004).

<sup>8</sup>I. Polishchuk, P. Ranade, T.-J. King, and C. Hu, IEEE Electron Device Lett. **22**, 444 (2001).

<sup>9</sup>I. Polishchuk, P. Ranade, T.-J. King, and C. Hu, IEEE Electron Device Lett. **23**, 200 (2002).

<sup>10</sup>D. S. Yu, C. H. Huang, A. Chin, C. Zhu, M. F. Li, B. J. Cho, and D.-L. Kwong, IEEE Electron Device Lett. 25, 138 (2004).

<sup>11</sup>V. Misra, H. Zhong, and H. Lazar, IEEE Electron Device Lett. 23, 354 (2002)

<sup>12</sup>T. Gougousia and G. N. Parsons, J. Appl. Phys. **95**, 1391 (2004).

<sup>13</sup>A. S. Killampalli, P. F. Ma, and J. R. Engstrom, J. Am. Chem. Soc. (accepted).

<sup>14</sup>N. L. Jeon, K. Finnie, K. Branshaw, and R. G. Nuzzo, Langmuir 13, 3382 (1997)

<sup>15</sup>R. Chen, H. Kim, P. C. McIntyre, and S. F. Bent, Appl. Phys. Lett. **84**, 4017 (2004).

<sup>16</sup>T. Aaltonen, P. Alen, M. Ritala, and M. Leskela, Chem. Vap. Deposition 9, 45 (2003).

<sup>17</sup>M. A. Alam and M. L. Green, J. Appl. Phys. **94**, 3403 (2003).

<sup>18</sup>R. Nyholm and N. Martensson, J. Phys. C **13**, L279 (1980).

<sup>19</sup>J. R. Hauser and K. Ahmed, *Characterization and Metrology for ULSI Technology*, AIP Conf. Proc. 449 (AIP, New York, 1998), pp. 235–239.

<sup>20</sup>R. Jha, J. Gorganos, Y. H. Kim, R. Choi, J. Lee, and V. Misra, IEEE Electron Device Lett. 25, 420 (2004).

<sup>21</sup>J. Tersoff, Phys. Rev. B **30**, 4874 (1984).

<sup>22</sup>Y.-C. Yeo, T.-J. King, and C. Hu, J. Appl. Phys. **92**, 7266 (2002).